XIX Workshop on Semiconductors and Micro & Nano Technology

# April 10-11, 2025 Centro Universitário FEI

campus São Bernardo do Campo

ISBN 978-65-89048-04-6

Organized by

Support

# Organized by CENTRO UNIVERSITÁRIO FEI

# SEMINATEC 2025 XIX WORKSHOP ON SEMICONDUCTORS AND MICRO & NANO TECHNOLOGY

# Support:

UNICAMP - Universidade Estadual de Campinas USP – Universidade de São Paulo IEEE – Advancing Technology for Humanity

April 10-11, 2025 Centro Universitário FEI, Campus São Bernardo do Campo

# Centro Universitário FEI.

XIX workshop on semicondutores and micros & nano technology – SEMINATEC 2025: 10 A 11 de abril de 2025, São Bernardo do Campo / Centro Universitário FEI – São Bernardo do Campo Universitários FEI, 2025. 123 f.; pdf

ISBN 978-65-89048-04-6

1. Semicondutores. 2. Microtecnologia. 3. Nanotecnologia. 4. Engenharia eletrônica. I. SEMINATEC 2025. II. Centro Universitário FEI. III. Título.

CDU: 621.381

# Preface

This volume compiles the papers presented at SEMINATEC 2025 – XIX Workshop on Semiconductors and Micro & Nano Technology held on April 10-11, 2025, at Centro Universitario FEI, Brazil.

There were 58 submissions selected for presentation at SEMINATEC 2025, as well as the presentations of six invited speakers, five of them Distinguished Lecturers of the IEEE Electron Devices Society: Dr. Adelmo Ortiz-Conde, from Universidad Simon Bolivar, Venezuela, giving the talk "On the MOSFET charge control modeling and the Lambert W Function"; Dr. Alvin Loke, from Intel, San Diego, USA, giving the talk "Impact of Advanced CMOS Technology on Analog Design"; Dr. Gilson Inacio Wirth, from Universidade Federal do Rio Grande do Sul, Brazil, giving the talk "Noise-induced Jitter of Signals in Synchronous Circuits"; Dr. João Antonio Martino, from Universidade de Sao Paulo, Brazil, giving the talk "FET100 - 100 years of Field Effect Transistors"; Dr. José Alexandre Diniz, from Universidade Estadual de Campinas, Brazil, giving the talk "Ultra-Thin and Thin Films for Nano and Micron Technologies"; Dr. Marcelo Antonio Pavanello, from Centro Universitario FEI, Brazil, giving the talk "Cryogenic Operation of Planar and Multigate Fully Depleted SOI MOSFETs".

We would like to express our gratitude to the authors as well as the reviewers.

We would like to acknowledge the IEEE EDS Student Chapter at Centro Universitario FEI, the USP IEEE/ED Chapter, and the USP IEEE/SSCS Chapter for inviting EDS Distinguished Lecturers who enlightened the Workshop.

April 10-11, 2025 São Bernardo do Campo

Rodrigo Trevisoli Doria – General Chair Renato Camargo Giacomini – Program Chair Local Organizing Committee: Fernando Jose da Costa Jaime Calçade Rodrigues Marcelo Antonio Pavanello Marcilei Aparecida Guazzelli Michelly de Souza Salvador Pinillos Gimenez

# Table of Contents

# Poster Session I

| Influence on Sensitivity as GCR Adjustment in ISFET Memory                                                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The BESOI Dual-Technology FET                                                                                                                                           |

| Analog Behavior of Nanosheet Transistor from Room Temperature to -100°C                                                                                                 |

| Application of Vertical Nanowire (VFET) in Transconductance Operational Circuits                                                                                        |

| A Multi-Phased Clock TDC of 500 MHz at 62.5 ps Developed in Cyclone-V FPGA                                                                                              |

| Design and Optimization of a CMOS Power Amplifier for 6 GHz Applications                                                                                                |

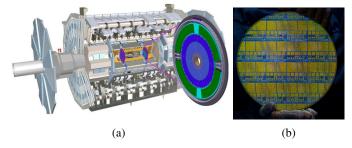

| Development of Low-Noise Amplifiers for the Detection of a Few Photons Using Silicon Photomultipliers                                                                   |

| Metallized Substrate Technologies – A Cost-effective Approach for RF Circuits and Photonic Packaging                                                                    |

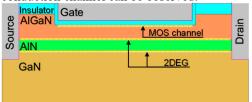

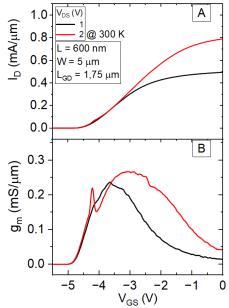

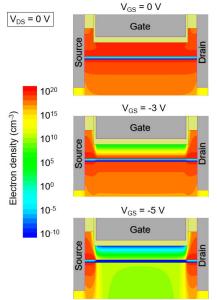

| Simulation-Assisted Analysis of Carrier Distribution in GaN-Based MISHEMT                                                                                               |

| Stress-Induced Modulation of the Schottky Barrier Height in Metal-Semiconductor Interfaces: Attaining Ohmic Contact by Pressure                                         |

| P. G. Serra Neto, K. S. Chi, and M. V. Puydinger dos Santos                                                                                                             |

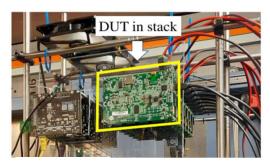

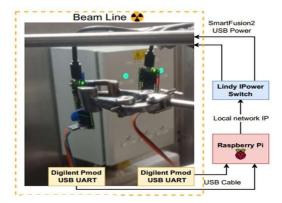

| Methodology for Monitoring Neutron-Induced Effects on FPGAs                                                                                                             |

| Electrical Degradation and Resistance Variation in Pseudo-Resistors for Harsh Environments                                                                              |

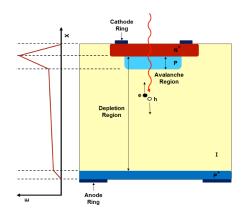

| Analysis of Low Gain Avalanche Detector (LGAD) Response to 10 keV X-Rays                                                                                                |

| Diffractive Structures Generated by Direct Laser Writing for Mapping Cutaneous Skin Lesions                                                                             |

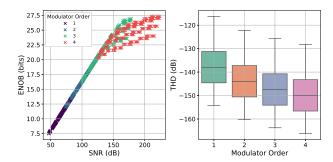

| Impact of Sample-Hold Circuit Non-Idealities on Sigma-Delta ADCs for Space Applications                                                                                 |

| AI-Optimized Sigma-Delta ADCs for Radiation-Tolerant Space Applications                                                                                                 |

| R. O. Nunes, A. C. C. Telles, M. C. Carlos, W. R. Melo, S. Finco, and L. E. Seixas Jr.                                                                                  |

|                                                                                                                                                                         |

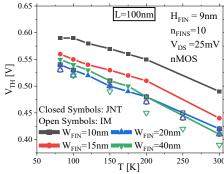

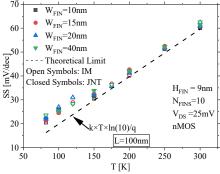

| R. O. Nunes, A. C. C. Telles, M. C. Carlos, W. R. Melo, S. Finco, and L. E. Seixas Jr.  Comparison of Inversion-Mode and Junctionless Nanowire SOI MOSFETs down to 82 K |

| P. Romano, M. Guazzelli, and R. Giacomini                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

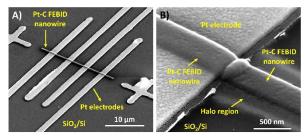

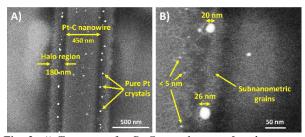

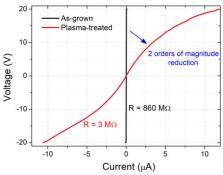

| Room-Temperature Oxygen Plasma-Based ex-Situ Purification of Pt-C FEBID Nanocomposites for Piezoresistance and Flexible Electronics Applications |

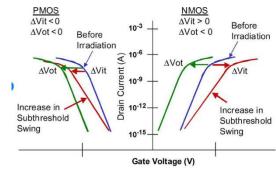

| Impact of TID Effects on Vth Variation in Power Transistors                                                                                      |

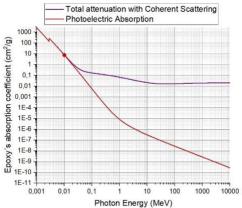

| Measurement of Total Dose Accumulated in Devices: Impact in Absorption by Encapsulation                                                          |

| Restarting the MIMEC lab at INPE                                                                                                                 |

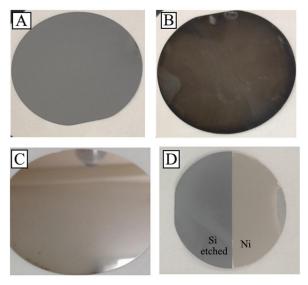

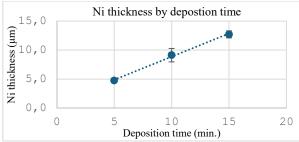

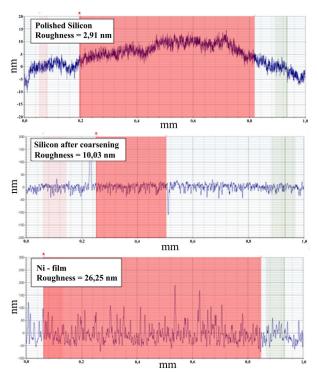

| Electroless and Electrolytic Deposition of Ni-P and Ni at Low Temperature on Polished Silicon                                                    |

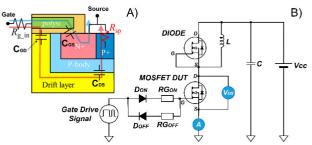

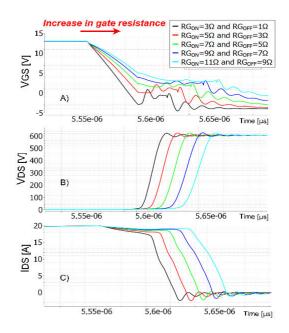

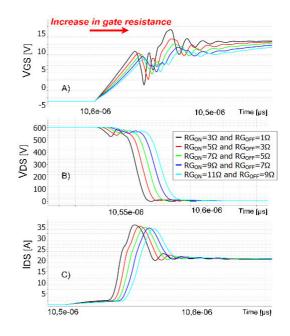

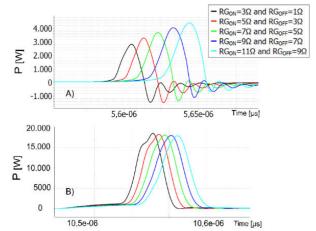

| A Review of the Impact of Gate Resistance on Switching Losses in SiC MOSFETs                                                                     |

| Impact of Gate-to-Fin Angle on GiD-FinFET Electrical Performance                                                                                 |

| Impact of TID on Power Transistors with Different Layouts                                                                                        |

| A study of Stress Behavior in Top-Down Fabricated Highly Strained Silicon Nanowires                                                              |

| Blade Coating as a Promising Tool for High Yield Photoresist Coating on Silicon Substrates                                                       |

| Impact of Thermal Effects on the Electrical Performance of AlGaN/GaN HEMTs                                                                       |

| Poster Session II                                                                                                                                |

| FET-Based Infrared Detector with Vanadium Oxide and Graphene Ribbons                                                                             |

| All-Fiber Compact Electromagnetic Taper Sensor: A Proposal                                                                                       |

| Review on the Use of RISC-V Processors for Space Applications Radiation Resilience and Fault-Tolerant Architectures                              |

| M. C. Carlos, S. Finco, R. O. Nunes, A. C. C. Telles, W. R Melo, and L. E. Seixas Jr.                                                            |

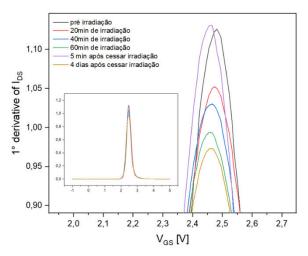

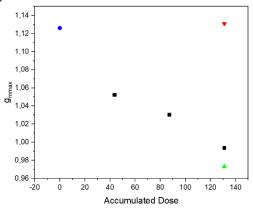

| Transconductance in a NMOS Power Transistor Under Ionizing Radiation Effects                                                                     |

| Evaluating the Impact of Ionizing Radiation on the Threshold Voltage of NMOS Power Transistors                                                   |

| Low Voltage Inverter Gate with Schmitt-Trigger Input Using TSMC 65 nm for a 12 Tracks Standard Cell                                              |

| TCAD Simulation of SOI Nanowire MOSFET Operating down to 30K                                                                                     |

| Fabrication of Through-Silicon Vias Using Laser Drilling                                                                                         |

| SpaceWire: Radiation Effect Error Injection                                                                                                      |

| Design of a Fully Differential OTA Miller with DDA Common Mode Feedback control using the gm/Id methodology                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L. B. Trujilho, V. N. D. Abreu, L. Compassi-Severo, and O. Saotome                                                                                                           |

| Design Methodology for Low-Voltage Low-Power LNTAs                                                                                                                           |

| OTA Design with SOI FinFET in SPICE Simulator. 90  P. H. Madeira and P. G. D. Agopian                                                                                        |

| SpaceLab - Maturing on Components Testing Against Radiation Exposure                                                                                                         |

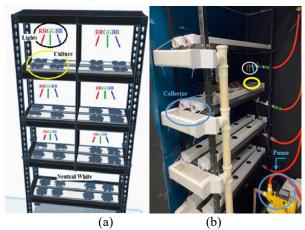

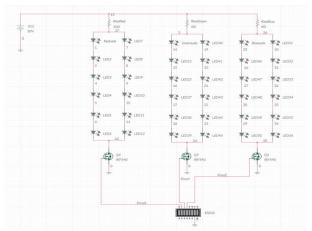

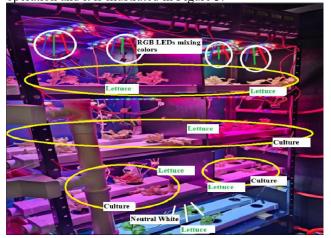

| Precise Lighting Electronic System Applied to Vertical Farming to Maximize Crop Growth Controlled and Monitoring by Free IoT Platforms                                       |

| New Perspectives on Body Biasing in Dickson Charge Pump Circuits with UTBB Transistors in Diode Mode96  E. T. Fonte, R. Trevisoli, and R. T. Doria                           |

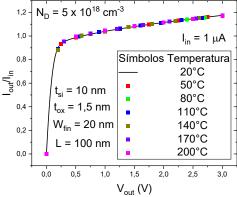

| Electrical Behavior of the HDM's ZTC Point in High-Temperature Range                                                                                                         |

| Electronic System With Images of Morphological Characterization of Crops                                                                                                     |

| Half-Octo Layout Style for Solar Cells                                                                                                                                       |

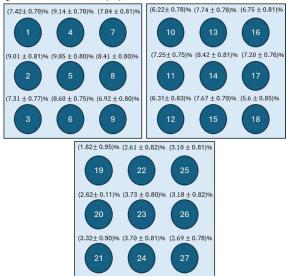

| Variability and Performance Analysis of Dual-Level Stacked Nanowire Transistors                                                                                              |

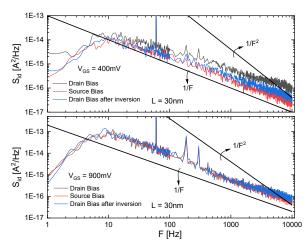

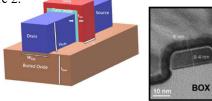

| Low-Frequency Noise Evaluation of Experimental Junctionless Nanowire Transistors for Different Biasing Conditions                                                            |

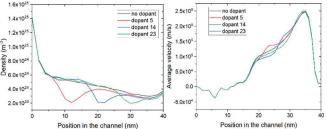

| Evaluation of the Impact of a Single Dopant Position into the Channel on the On-Current of Nanowire Transistors through Atomistic Simulations                                |

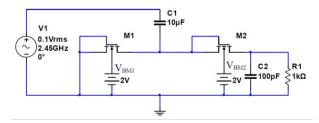

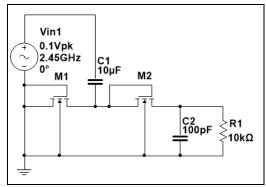

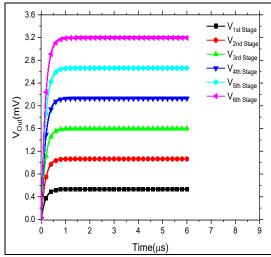

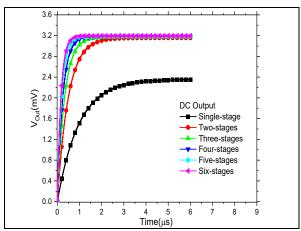

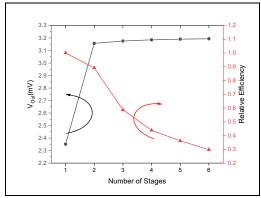

| Design of Multi-Stage Architecture in Dickson-Based RF-DC Rectifiers for Energy Harvesting Applications 110  M. T. M. Sabatine, R. Trevisoli, G. S. Pereira, and R. T. Doria |

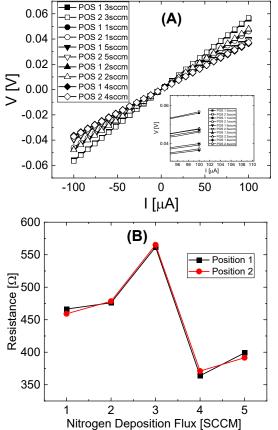

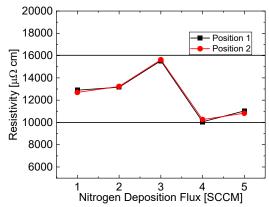

| Process Characterization of TiN Deposition for Obtaining Metallization Contacts for ReRAM Devices                                                                            |

| Junctionless Nanowire Transistor-Based Current Mirror in High-Temperature Applications                                                                                       |

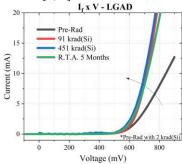

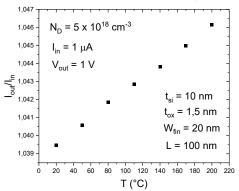

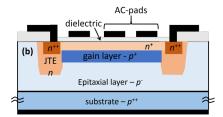

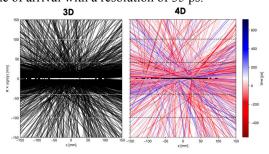

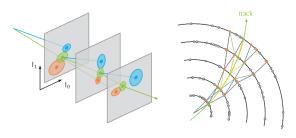

| Ultra-Fast Semiconductor Detectors for Radiation Sensing in High-Energy Physics and X-Ray Synchrotron Applications                                                           |

| 4D Tracking with Semiconductor Sensors for Particle Physics: from Signal Processing Techniques to Deep Learning Approaches                                                   |

| Automation of Electrical Transport Measurements                                                                                                                              |

# Influence on Sensitivity as GCR adjustment in ISFET Memory

H. L. Carvalho\*, R. C. Rangel and J. A. Martino LSI/PSI/USP, University of Sao Paulo, Sao Paulo, Brazil \*e-mail: hen.lanfredi@usp.br

### 1. Abstract

This work investigates the operation of ISFET Memory devices, which combine the ion sensitivity of ISFETs with the charge storage capabilities of floating-gate transistors. Two device designs are compared: an unadjusted configuration with a Gate Capacitance Ratio (GCR) of 0.22 and an adjusted design achieving a GCR of 0.57. The adjusted device demonstrates improved performance, including reduced write/erase voltages, faster charge times, and expanded operational range in the hole-write mode between pH 6 and 8. Sensitivity measurements reveal a peak of 940 mV/pH in the unadjusted device and 1609 mV/pH in the adjusted device. These results show the ISFET Memory's versatility as a pH sensor with tunable sensitivity, suitable for applications in biosensing and environmental monitoring.

### 2. Introduction

Over the past few decades, the continuous evolution in microelectronics and nanoelectronics has propelled the development of advanced electronic devices and sensor technologies [1]. One notable CMOS-based sensor is the Ion-Sensitive Field-Effect Transistor (ISFET), which has been extensively explored for detecting biological and ionic signals with applications ranging from medical diagnostics to analytical chemistry. [2,3] The ISFET's inherent compatibility with CMOS technology facilitates mass production and integration into complex circuits, enhancing its versatility in real-time monitoring applications [2,3].

The Memory ISFET architecture has emerged as a promising solution. By combining the ion sensitivity of ISFETs with the charge storage capabilities of floating-gate transistors commonly used in non-volatile memory devices like USB drives and SSDs with Floating Gate ISFETs effectively isolate the analyte from the logic circuits while maintaining compatibility with MOS manufacturing processes [5].

A critical factor influencing the performance of FG-ISFETs lies in the optimization of the Gate Capacitance Ratio (GCR), which directly impacts key parameters such as memory window, write/erase efficiency, and device sensitivity [6]. Although the dielectric material used in the gate plays a significant role in determining ISFET sensitivity, traditional materials like SiO<sub>2</sub> are often limited by low stability and sensitivity [7]. Alternative materials such as Al<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub>, HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, and ZrO<sub>2</sub> have been explored to address these limitations, yet the theoretical sensitivity of ISFETs remains capped at approximately 60 mV/pH [8]. This work focuses on comparing the sensitivities achieved in previously simulated ISFET Memory designs and ideal ISFETs while also presenting their modes of operation, including write, erase, and read processes.

## 3. Devices characteristics and operations

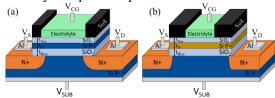

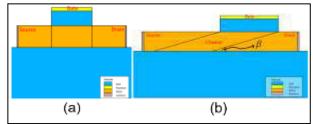

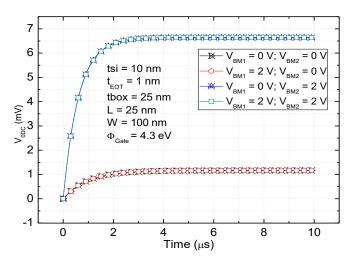

The first ISFET Memory [9], shown in Fig. 1 (a), design is based on an Ultra-Thin Body and Box Silicon-On-Insulator (UTBB SOI) structure, achieving a Gate Capacitance Ratio

(GCR) of approximately 0.22. The device features a 25 nm buried oxide layer (SiO<sub>2</sub>) as the bottom oxide, and a 6 nm SiO<sub>2</sub> layer as the top oxide. The floating gate and substrate are composed of silicon <100> doped with boron at a concentration of 10<sup>15</sup> atoms/cm<sup>-3</sup>. The second device, shown in Fig. 1 (b), were made using TCAD Synopsys Sentaurus [10] to improve GCR, by reducing the effective area between the top oxide and electrolyte, reducing de top capacitance, combined with doping the floating gate at 10<sup>20</sup> atoms/cm<sup>-3</sup> to enhance conductivity and optimize capacitance.

Fig. 1. Memory ISFET unadjusted (a) and unadjusted (b).

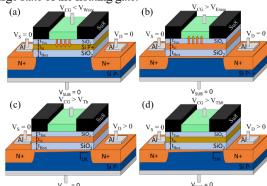

The ISFET Memory operates similarly to a nonvolatile semiconductor memory based on Fowler-Nordheim tunneling, with the top oxide layer functioning as the tunneling oxide. Its operation can be divided into three operation modes, in Fig. 2: (i) Writing electrons (Fig. 2 (a)): By applying a high negative voltage to the control gate, electrons tunnel into the floating gate, resulting in a negative charge ( $Q_{FG} < 0$ ) stored within it. (ii) Writing holes (Fig. 2 (b)): This mode removes stored electrons ( $Q_{FG} \approx 0$ ) and could introduces holes into the floating gate, creating a positive charge ( $Q_{FG} > 0$ ). (iii) Read Operation (Fig. 2 (c) and (d)): The state of the device, whether in the written or erased condition, is determined by applying specific control gate ( $V_{CG}$ ) and drain-source ( $V_{DS}$ ) voltages. The resulting drain current ( $I_{DS}$ ) is then monitored to identify the charge state of the floating gate.

Fig. 2. Memory ISFET, writing electrons (a) and holes (b), programmed with electrons (c) and holes (d).

## 4. Results and discussion

The charge stored in the floating gate after the write operation, involving electrons or holes, becomes dependent on the interface potential [9]. Consequently, the floating gate charge varies with the hydrogen ion concentration, enabling the ISFET Memory to act as a pH sensor. This functionality arises from the interaction between the floating gate and the solution,

where the potential of the interface affects the tunneling effect during the writing operation.

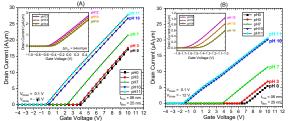

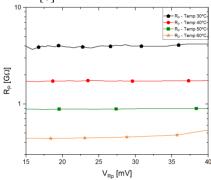

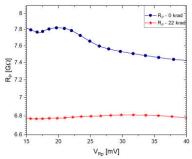

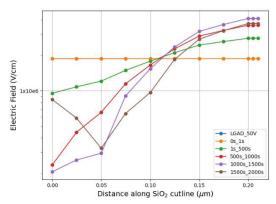

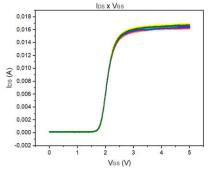

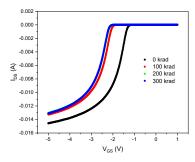

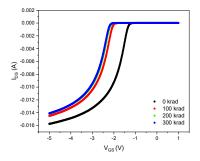

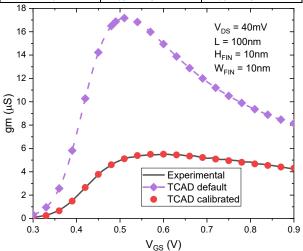

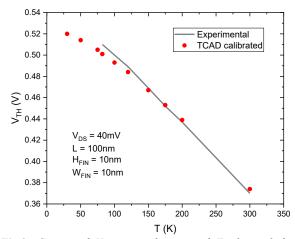

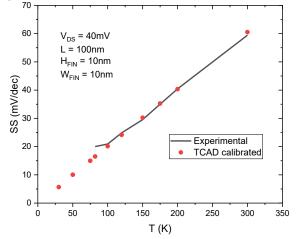

The first device requires high write and erase voltages due to its low gate capacitance ratio (GCR) of approximately 0.22. Fig. 3 (a) shows the drain current ( $I_{DS}$ ) as a function of the control gate voltage ( $V_{CG}$ ) for pH values ranging from 0 to 14 before the capacitance adjustment. Fig. 3 (b) illustrates the results after the adjustment, which improves the GCR to approximately 0.57. In both cases, a rebound effect is observed in the threshold voltage ( $V_{Th}$ ). Specifically, there is a region where an increase in pH (or decrease in [ $H^+$ ] concentration) leads to a linear increase in the threshold voltage, resembling the behavior of ISFETs. However, another region at higher pH levels, a nonlinear behavior emerges, with the threshold voltage decreasing. This behavior arises from the floating gate charge's dependence with the interface potential, resulting in faster charging at higher [ $H^+$ ] concentrations.

A similar behavior is observed in both devices in the hole-write mode, where the rebound effect is also present. However, the linear region of sensitivity is shifted to acid pH values due to the difficulty of storing holes in the floating gate at these pH levels. Additionally, in the second device, for both writing modes, a significant reduction in write/erase voltage and charge time is observed, attributed to the improved GCR. The threshold voltage for both devices was extracted using the [11] method to compare their sensitivity after the capacitance adjustment.

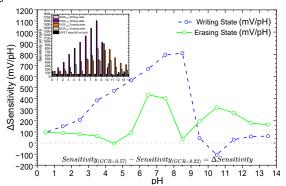

For both cases, the sensitivity of the device can be defined similarly to that of a traditional ISFET, where sensitivity is the absolute change in threshold voltage per unit of pH. However, ISFET Memory exhibits two types of sensitivity: one in the programmed holes mode and the other in the programmed electrons mode. Fig. 4 illustrates the sensitivity as a function of pH for the ISFET Memory, comparing unadjusted and adjusted devices in both modes.

Fig.3. Drain current as a function of the control gate voltage for pH values ranging from 0 to 14 before (a) and after (b) the capacitance adjustment.

Fig.4. Sensitivity as a function of pH values on ISFET Memory unadjusted and adjusted writing with electrons and holes.

The average sensitivity observed in the unadjusted transistor is 264 mV/pH, with a peak sensitivity of 910 mV/pH in the programmed electrons mode, occurring between pH 9 and 10. In contrast, the adjusted transistor demonstrates an average sensitivity of 501.8 mV/pH, with a peak sensitivity of 1609 mV/pH between pH 8 and 9. With the capacitance adjustment, there is an increase in both average and maximum sensitivity, remaining superior to the sensitivity limit of traditional ISFETs across its entire range. This performance could be improve achieved by utilizing the hole write mode for high pH levels and the electron write mode for pH values below 10

Furthermore, the capacitance adjustment significantly improved the hole write mode performance between pH 6 and 8, effectively expanding its operational range. This result is particularly noteworthy because the sensitivity becomes variable with the gate capacitance ratio, demonstrating the device's tunability. Such flexibility makes the ISFET Memory a promising candidate for a wide range of pH-sensing applications, including biosensors and environmental monitoring.

## 5. Conclusion

This study introduced the ISFET Memory, demonstrating its superior performance compared to traditional ISFETs by highlighting the influence of the gate capacitance ratio on device sensitivity. Its adjustment resulted in a increases in average and peak sensitivity, however, the device still maintained superior performance. While the average sensitivity increased, the adjusted transistor also enabled reduced write/erase voltages and improved sensitivity between pH 6 and 8 in its hole write mode. Across the full pH range, the device exhibited sensitivity superior to traditional ISFETs, with a peak sensitivity of 1609 mV/pH between pH 8 and 9.

## 6. Acknowledgments

The authors acknowledge CNPq, CAPES (Coordenação de Aperfeiçoamento de Pessoal de Nível Superior – Brazil - Finance Code 001) and São Paulo Research Foundation - FAPESP (under grant #2020/04867-2) for the financial support.

- [1] S. Cao, et al., Electrochem Sci Adv., 3, 2023.

- [2] D. Tran et al., Materials, 11, 2018.

- [3] O. Gubanova et al., Materials Science in Semiconductor Processing, 2024.

- [4] S. S. Nemati et al., IEEE Sensors Journal, 24, 2024.

- [5] Wang S, et al., Adv Electron Mater, 2019.

- [6] T. Cong, et al., Ain Shams Engineering Journal, 14 2023.

- [7] Jeon, J. H. et al., Science and Technology of Advanced Materials, 21, 2021.

- [8] P. Bergveld, Sensors and Actuators B: Chemical, 88, 2003

- [9] H. L. Carvalho 38th Symposium on Microelectronics Technology and Devices (SBMicro), 2024.

- [10] Synopsys TCAD, Sentaurus Device User Guide, (Version L2016.03).

- [11] A. O. Conde, et al., Microelectronics Reliability, 53, 2013.

# The BESOI Dual-Technology FET

P. H. Duarte, C. A. B. Mori, R. C. Rangel, and J. A. Martino

LSI/PSI/USP, University of Sao Paulo, Sao Paulo, Brazil e-mail: phduarte@usp.br

## **Abstract**

This work presents a fabrication and the experimental results of the BESOI MOSFET operating as two different technologies within a single transistor, referred to as the Dual-Technology FET (DT-FET). This transistor extends the reconfigurability beyond that of the traditional BESOI MOSFET, which only allows switching between n-type and p-type operation. By incorporating a single N<sup>+</sup> doping region and utilizing substrate biasing (Programming Gate), the DT-FET can function as an nMOSFET when a positive Programming Gate voltage is applied and as a pTFET when a negative Programming Gate voltage is applied.

## 1. Introduction

In recent years, advancements in reconfigurable transistors have led to the development of various structures and technologies [1,2]. The Back-Enhanced Silicon-On-Insulator MOSFET (BESOI MOSFET), patented in 2015 [3], was proposed as a solution for designing reconfigurable transistors with reduced fabrication complexity [3]. Its simple fabrication process and reliance on Programming Gate biasing enable it to switch between n-type and p-type operation.

This functionality is possible because the device includes a buried oxide layer that isolates the silicon channel from the substrate, allowing the manipulation of charge carriers through the Programming Gate. By applying a voltage to the substrate, an electric field is generated, inducing carriers within the channel through a mechanism known as electrostatic doping [4].

Therefore, this study presents a novel form of reconfigurability, expanding beyond simply altering the device type to modifying its primary conduction mechanism. Rather than transitioning solely between nMOS and pMOS modes, a device capable of switching between nMOS and pTFET (p-type Tunnel FET) operation was experimentally investigated.

# 2. Fabrication Process

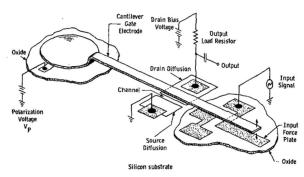

The devices were fabricated at the Integrated Systems Laboratory (LSI) of the University of Sao Paulo (USP). A silicon-on-insulator (SOI) wafer was used as the sample substrate, featuring a doping concentration of  $10^{15}$  cm<sup>-3</sup>, a buried oxide layer with a thickness of 200 nm, and a 20 nm silicon layer on top of the insulator. A wet oxidation step was performed to obtain a gate oxide approximately 10 nm thick. To enable the device to operate under two technologies, both as an nMOSFET and a pTFET, phosphorus doping at a concentration of

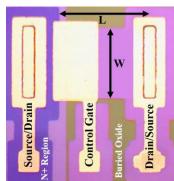

$10^{20}~cm^{-3}$  was applied to one side (source/drain) of the silicon channel film. For contact formation, aluminum deposition was carried out, resulting in a device with a channel length and width of 290  $\mu m$  and 210  $\mu m$ , respectively. The fabrication result is presented in the Fig.1.

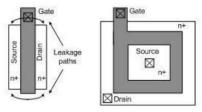

Fig.1. Photo of the fabricated Dual-Technology FET.

## 3. Working Principle

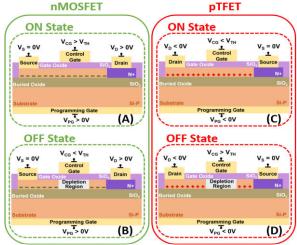

As previously mentioned, the substrate bias (Programming Gate) determines the device type due to the electrostatic doping effect. If a sufficiently positive voltage is applied ( $V_{PG} > 0V$ ), an electron channel is induced in the silicon film just above the buried oxide (second interface), causing the device to operate as an nMOSFET.

The gate contact (Control Gate) regulates the device state, switching it between on and off. If the voltage applied to the Control Gate ( $V_{CG}$ ) exceeds the threshold voltage ( $V_{CG} > V_{TH}$ ), the device turns on (Fig.2-A), allowing current to flow when a positive potential difference between the source and drain is present ( $V_{DS} > 0V$ ). Conversely, if  $V_{CG}$  is lower than the transistor's threshold voltage ( $V_{CG} < V_{TH}$ ), the device remains off (Fig.2-B).

It is important to emphasize that, in this first case, the doped (N<sup>+</sup>) region on the wafer serves as the drain contact. This configuration is necessary to ensure that the biasing maintains the PN junction between the channel and the doped region in a reverse biased condition, thereby allowing current conduction.

A similar process occurs in the case of the pTFET. If a sufficiently negative voltage is applied ( $V_{PG} < 0V$ ), a hole channel is induced at the second interface of the channel, causing the device to operate as a pTFET. Just like in the nMOSFET configuration, the Control Gate regulates the device state, switching it between on and off. If the voltage applied to the Control Gate ( $V_{CG}$ ) is

lower than the threshold voltage ( $V_{CG} < V_{TH}$ ), the device turns on (Fig.2-C), allowing current flow when a negative potential difference between the source and drain is present ( $V_{DS} < 0V$ ). Conversely, if  $V_{CG}$  is higher than the transistor's threshold voltage ( $V_{CG} > V_{TH}$ ), the device remains off (Fig.2-D).

However, unlike the nMOSFET, the PN junction between the channel and the doped region must be reverse-biased to enable band-to-band tunneling (BTBT), allowing the transistor to function as a tunnel FET. To achieve this, the contact placed on the doped region serves as the Source, enabling carrier tunneling from the channel to the Source.

Fig. 2. Schematic drawing of the operation principle for the device working as nMOSFET (left side) and pTFET (right side).

## 4. Results and discussion

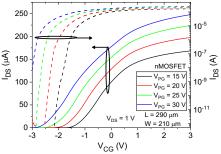

The results obtained for the Dual-Technology FET (DT-FET) are presented in this section. It is important to emphasize that these results correspond to both nMOSFET and pTFET operation within the same device, meaning that the geometric characteristics remain identical. As a result, the transistors are asymmetric and exhibit different current levels, primarily due to the distinct conduction mechanisms involved. The curve in Fig. 3 illustrates the drain current as a function of the Control Gate voltage when the device operates as an nMOSFET.

Fig.3. The Drain current as a function of the Control Gate voltage for the nMOSFET for different Programming Gate voltages.

In Fig. 3 is possible to observe the expected dependency between Programming Gate bias and threshold voltage, consistent with the behavior of a

traditional <sup>BE</sup>SOI MOSFET. It is important to note that, despite being fabricated using a simplified process, the results confirm that the device operates as expected.

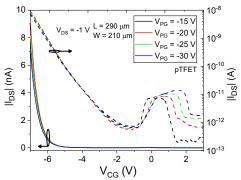

Fig. 4 illustrates the drain current as a function of the Control Gate voltage when the device operates as an pTFET.

Fig. 4. The Drain current as a function of the Control Gate voltage for the pTFET for different Programming Gate voltages.

The Fig.4 demonstrates that the device is working as pTFET. However, the Programming Gate voltage has no high influence on the device threshold voltage, due the tunneling mechanism, which occurs on the channel/Source junction. Furthermore, no ambipolar current is observed in the graph and only a minimal variation with respect to the Programming Gate bias is detected on off state region. This occurs due to the underlap region between the Control Gate and the Drain, which does not allow an ambipolar current to arise on this side.

## 5. Conclusions

The results presented confirm that this device, with its simple fabrication process, can seamlessly operate as either an nMOSFET or a pTFET by merely adjusting the applied bias. Since the device is fabricated in silicon using a fully CMOS-compatible process a potential future application would be its use as a MOSFET for digital circuits and a TFET for analog circuits.

## **Acknowledgments**

The authors would like to thank FAPESP, CAPES and CNPq for the financial support.

- [1] G. Galderisi, T. Mikolajick and J. Trommer, "The RGATE: An 8-in-1 Polymorphic Logic Gate Built From Reconfigurable Field Effect Transistors," in IEEE Electron Device Letters, vol. 45, no. 3, pp. 496-499, March 2024.

- [2] L. Wind et al., "Reconfigurable Si Field-Effect Transistors With Symmetric On-States Enabling Adaptive Complementary and Combinational Logic," in IEEE Transactions on Electron Devices, vol. 71, no. 2, pp. 1302-1307, Feb. 2024.

- [3] J. A. Martino, R. C. Rangel, "Transitor Fabrication Method of BESOI MOSFET" Patent n. BR 10 2015 020974 6 B1, 2015. [4] G. Gupta, B. Rajasekharan and R. J. E. Hueting, "Electrostatic Doping in Semiconductor Devices," in IEEE Transactions on Electron Devices, vol. 64, no. 8, pp. 3044-3055, Aug. 2017.

# Analog Behavior of Nanosheet Transistor from Room Temperature to -100°C

T. G. Pereira<sup>1</sup>, J. A. Martino<sup>1</sup> and P. G. D. Agopian<sup>1,2</sup>

<sup>1</sup> LSI/PSI/USP, University of Sao Paulo, Sao Paulo, Brazil

<sup>2</sup> UNESP, Sao Paulo State University, Sao Joao da Boa Vista, Brazil

e-mail: thaina.pereira@usp.br

## 1. Abstract

This study presents the experimental analysis of a Gate-All-Around (GAA) device, specifically a vertically stacked nanosheet transistor (NSH). The transistor's behavior was evaluated from room temperature down to -100 °C, based on experimental device's electrical characteristics. The transfer and output curves are exhibited, along with the threshold voltage (V<sub>T</sub>) values at different temperatures. Additionally, the transistor's efficiency  $(g_m/I_{DS})$  is discussed, considering the influence of mobility and subthreshold slope (SS). Finally, the intrinsic gains (A<sub>V</sub>) improvement with the temperature reduction is obtained, reaching 40 dB for the nMOS device and 46 dB for the pMOS device at -100°C.

### 2. Introduction

Gate-all-around nanosheet field-effect transistors (GAA NSFETs) have become a key solution for sub-5nm technology nodes. With vertically stacked, wide, thin nanosheet channels, NSFETs enable high drive currents and improved electrostatic control, allowing for further gate length scaling. Their width can be varied within the same wafer for design flexibility [1-4]. This device is applicable in both digital and analog applications.

This work examines the nanosheet (NSH) transistor, a GAA device featuring vertically stacked thin channels completely surrounded by gate material. This configuration helps minimize the device's footprint, reduces the body effect, and leads to lower leakage currents while enhancing the electrostatic coupling between the gate and the channel [5].

However, little focus has been given to analog applications under varying temperatures. This work aims to provide a comprehensive evaluation of n-type and p-type nanosheet transistors, comparing their performance from room to low temperatures. In the other works it's possible to compare this structure with higher temperature [6].

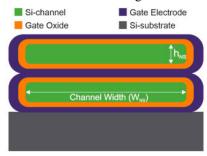

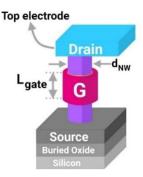

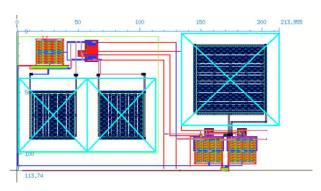

## 3. Device characteristic

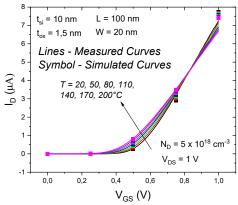

The GAA-NSH transistors analyzed in this study were fabricated at imec, Belgium, with the schematic structure shown in Fig. 1. The device consists of two stacked nanosheets and 22 parallel fins. The nanosheets have a rectangular shape with dimensions as follows: a NSH width ( $W_{\rm NS}$ ) of 15 nm, a NSH height ( $H_{\rm NS}$ ) of 11nm, a channel length of 100 nm, and an effective gate oxide thickness (EOT) of 0.9 nm. In this research, the devices were measured over a temperature range from 27 °C to -100 °C to assess their analog characteristics. The modeled Verilog-A was used to simulate the NSH device in Cadence to compare with experimental method.

## 4. Results and discussion

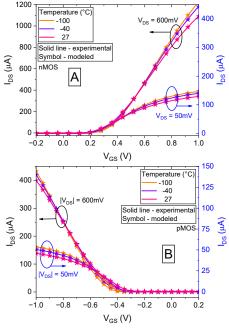

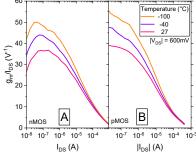

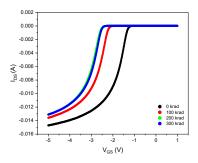

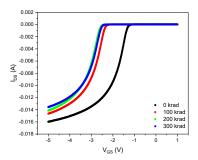

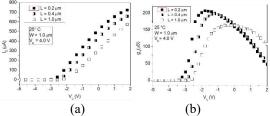

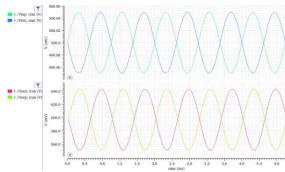

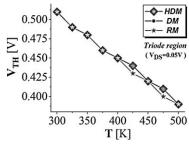

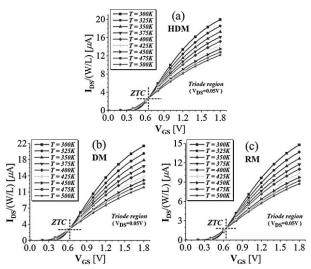

Fig. 2 presents the drain current as a function of gate voltage for both nMOS and pMOS devices at different temperatures, ranging from room temperature to -100°C, for both model and experimental data.

Additionally, it is possible to observe, both for the

$V_{\rm DS} = 50$  mV and the  $V_{\rm DS} = 600$  mV curves. The zero-temperature coefficient (ZTC) point, where temperature variation does not affect the drain current ( $I_{\rm DS}$ ) value.

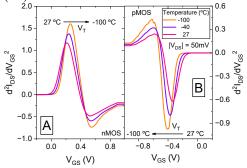

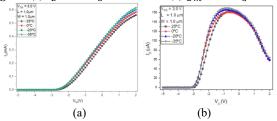

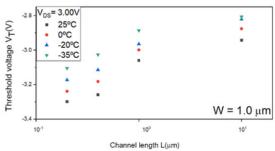

As the temperature decreases, due to the increase in device carrier mobility for both nMOS and pMOS, there is an increase in the magnitude of the threshold voltage  $(V_T)$ , which can be observed in Fig. 3.

Fig. 1 - Device Structure [6]

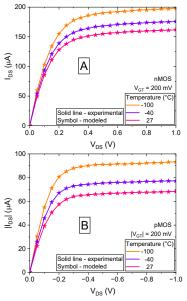

After identifying the  $V_T$  value for each temperature in Fig. 3, which shows increases due to the variation in the Fermi potential, an increase in carrier mobility is observed, resulting in a higher  $I_{DS}$ . The  $I_{DS}$  x  $V_{DS}$  relationship shown in Fig. 4 is then obtained.

In Fig. 4, are represent the drain current as a function of drain voltage for nMOS and pMOS devices. In both cases (Fig. 2 and Fig. 4), the experimental results and the modeled ones exhibit a strong agreement.

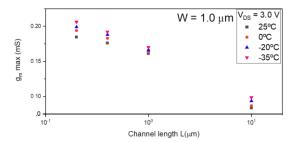

Fig 2 - Drain current as a function of gate voltage of NSH nMOS (A) and pMOS (B)

The transistor efficiency  $(g_m/I_{DS})$  as a function of the  $I_{DS}$  value for nMOS and pMOS is shown in Fig. 5, from

room temperature to -100 °C. In the weak inversion region, it can be observed that as the temperature decreases, there is an increase in the value of  $g_m/I_{DS}$ , as it is directly influenced by the inverse of subthreshold slope (SS).

Fig 3 – Threshold voltage of NSH nMOS (A) and pMOS (B) for different temperatures

In the strong inversion region, the main influence is related to the increase in carry mobility as the temperature decreases, because the effective mobility is only slightly changed since it is already degraded by series resistance and electric field.

Fig 4 - Drain current as a function of drain voltage of NSH nMOS (A) and pMOS (B)

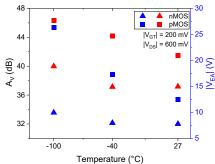

Using the experimental values from Fig. 4 in the  $|V_{DS}|$  range between 0.5 and 0.7 V, the Early Voltage ( $V_{EA})$ values can be extracted. By applying the equation  $A_V =$  $g_m/I_{DS}$  \* V<sub>EA</sub>, the intrinsic gain for each device and temperature is obtained. These values are presented in Fig. 6.

Fig 5 – Transistor efficiency of NSH nMOS (A) and pMOS (B) for different temperatures

As the temperature decreases, both parameters increase. The factors that affect the  $V_{EA}$  value in opposite ways with the temperature decrease are the increase in drain current and the improved slope of the I<sub>DS</sub> saturation

Since the temperature variation in strong inversion does not significantly affect the value of  $g_m/I_{DS}$ , the value of A<sub>V</sub> is more influenced by the value of

Fig 6 - Intrinsic voltage gain (red) and Early voltage (blue) as a function of temperature of nMOS and pMOS devices

#### Conclusions

This work presents a GAA transistor with two stacked NSH and 22 parallel fins, analyzing its electrical characteristics. GAA\_NSH were modeled using Verilog-A language based on experimental measurements and the transfer and output curves show a good agreement between experimental and modeled results. The device was subjected to different temperatures (from room temperature to -100 °C). As the temperature decreases, the magnitude of V<sub>T</sub> increases due to the Fermi potential variation, the carrier mobility increase resulting in a higher I<sub>DS</sub>, and SS value is reduced (enhance) due to the direct relation with temperature. In weak inversion the efficiency of the transistor increases as the temperature decreases, due to the influence of 1/SS. However, in strong inversion, temperature variation has no significant impact because the effective mobility is only slightly changed since it is already degraded by series resistance and electric field. The Av value increases as the temperature decreases, ranging from 37-39 dB for nMOS and 41-46 dB for pMOS following the  $V_{EA}$  tendency.

## Acknowledgments

The authors acknowledge CNPq, CAPES (Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brazil - Finance Code 001) and São Paulo Research Foundation -FAPESP (under grant #2020/04867-2) for the financial support, and imec for supplying the devices.

- G.E. Moore, Cramming More Components onto Integrated Circuits, in Proceedings of the IEEE, vol. 86, no. 1, pp. 82-85, Jan. 1998, doi: 10.1109/JPROC.1998.658762.

- Cutress, I. IBM Creates First 2nm Chip. Anandtech, https://www.anandtech.com/show/16656/ibm-creates-first-2nm-chip; 2021 [accessed: Fev 12

- 2025]. Taiwan Semiconductor Manufacturing Company, technonlogy, 3nm technonlogy, https://www.tsmc.com/english/dedicatedFoundry/technology/logic/1 3nm; 2021 [accessed Fev. 12, 2025]. Koyama M, et al. Solid-State Electron. 2013; 84:46–52, doi: 10.1016/j.sse.2013.02.024 Veloso A, et al. J Phys: Condens Matter 2018, doi: 10.1088/1361-648x/ aad7c7. Silva V. C. P., et al. Solid-State Electronics, vol. 208, no. 108729, October 2023, doi: 10.1016/j.cse.2023.108729

- 4.

- 5.

- 10.1016/j.sse.2023.108729.

# Application of Vertical Nanowire (VFET) in Transconductance Operational Circuits

A. R. Ribeiro<sup>1</sup>, Vanessa C.P. Silva<sup>2</sup>, J. A. Martino<sup>1</sup> and P. G. D. Agopian<sup>1,3</sup>

<sup>1</sup> LSI/PSI/USP, University of Sao Paulo, Sao Paulo, Brazil

<sup>2</sup> SEL/USP, University of Sao Paulo, Sao Carlos, Brazil

<sup>3</sup> UNESP, Sao Paulo State University, Sao Joao da Boa Vista, Brazil

e-mail: arllen@usp.br

## 1. Abstract

The search for low-power and high-performance analog circuits has driven research into new transistor technologies. This work investigates the use of Vertical Nanowire Field-Effect Transistors (VFETs) in a two-stage OTA. VFETs offer a low threshold voltage (0.15V), high intrinsic gain (34.87 dB), and favourable transconductance (1.61 mS), enabling operation at 1.8 V with reduced power consumption. The designed of an amplifier transconductance operational circuit (OTA) achieved a 44 dB voltage gain and a 986 MHz GBW, demonstrating VFETs' potential for high-speed and low-power analog applications.

## 2. Introduction

Research on electronic devices focuses on achieving more compact and efficient designs. However, as device dimensions shrink, short-channel effects degrade performance. To address these challenges, studies explore innovative strategies to mitigate these effects. [1].

The VFET device stands out among new device designs, offering strong electrostatic coupling that enhances performance and enables nanoscale operation. [2]. Recent studies show that these devices offer better electrostatic coupling, improved short-channel control, and higher switching speeds, enabling operation at 3 to 5nm nodes. [3].

The objective of this work is to evaluate the main electrical parameters of vertical nanowire devices and assess their potential when applied in an amplifier transconductance operational circuit.

## 3. Devices characteristics and circuit

Fig. 1 - Device Structure.

The VFET used in this study is a p-type device

fabricated at Imec, Belgium, on an SOI wafer. It features a 145 nm buried oxide, 50 nm gate length, 20 nm channel diameter, 400 parallel nanowires, and a gate dielectric with a 0.9 nm equivalent oxide thickness. The chosen configuration was the forward mode, with the source as the bottom electrode. Additional fabrication details are in reference [4].

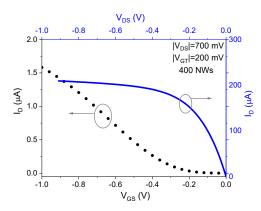

## 4. Results and discussion

The transfer curves of the V-pFETs, presented in the Fig.2, were measured using the Keysight® B1500A, applying a gate bias ( $V_G$ ) ranging from 0.5 V to -1.0 V in -10 mV steps. The drain voltage ( $V_{DS}$ ) was set to -50 mV for the triode region and -700 mV for the saturation region. The output characteristics were obtained by sweeping  $V_{DS}$  from 0 V to -1.0 V in -10 mV steps, considering a gate overdrive voltage of |200 mV|.

Fig. 2 - Drain current as a function of gate voltage (left and down axes) and drain voltage (right and up axes).

Table 1 presents the main electrical parameters of the VFET.

Table 1 – Electrical Parameters

| Electrical Parameters       |        |  |  |  |

|-----------------------------|--------|--|--|--|

| Threshold Voltage (V)       | 0.15   |  |  |  |

| Drain Current (μA)          | 7.89   |  |  |  |

| Transconductance (mS)       | 1.61   |  |  |  |

| Output Conductance (mS)     | 0.0281 |  |  |  |

| Early Voltage (V)           | 6.13   |  |  |  |

| Intrinsic Voltage Gain (dB) | 34.87  |  |  |  |

The VFET has a moderate Early voltage ( $V_{EA}$ ) of |6.13V| and low output conductance (0.0281 mS), leading to a high intrinsic voltage gain (Av) of 34.87 dB, which is beneficial for analog applications. The high

transconductance  $(g_m)$  boosts signal amplification, while the low output conductance  $(g_D)$  improves output resistance. Despite some channel modulation effects indicated by the Early voltage, the device shows good current control and amplification.

The study of output conductance is essential in analog circuits as it impacts electrical behavior and amplifier efficiency. Higher output conductance can degrade linearity and frequency response. The VFET was chosen for its favorable characteristics, including high intrinsic voltage gain, low output conductance, and moderate Early voltage, ensuring strong signal amplification with minimal degradation. Its high transconductance maximizes gain efficiency, improving linearity, frequency response, and current control, making it ideal for high-performance analog applications [5].

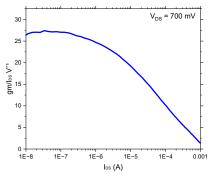

The method chosen for the projection of the OTA was the method gm/I<sub>D</sub>, the Fig. 3 shows the curve of gm/I<sub>D</sub> of the VFET device. The gm/I<sub>D</sub> curve for V<sub>DS</sub>=700mV shows high efficiency at low currents, making the VFET suitable for low-power applications. As I<sub>DS</sub> increases, gm/I<sub>D</sub> gradually decreases, indicating a transition to strong inversion. For gm/I<sub>D</sub>=8 V<sup>-1</sup>, the drain current is  $33\mu A$  with 400 nanowires in parallel, balancing gain and power consumption.

Fig. 3 - Transistor efficiency for VFET device.

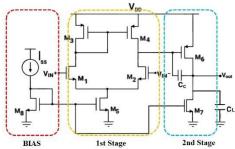

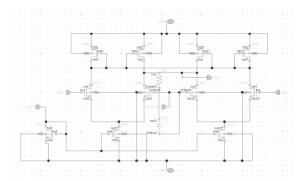

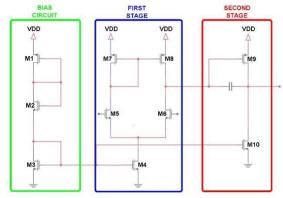

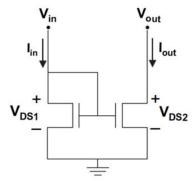

The Fig. 4 shows the schematic of the Two-Stage OTA used in this work.

Fig. 4 - OTA circuit Schematic

The design assumes similar behavior for nMOS and pMOS devices. It consists of two stages: the first stage includes a differential pair (M1, M2) with an active load (M3, M4), while the second stage features a commonsource amplifier (M6). The current mirror is made up of M8, M5, and M7, and the circuit also includes a compensation capacitor (Cc) and a capacitive load (C<sub>L</sub>).

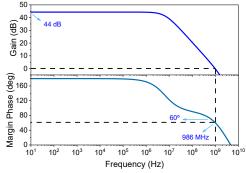

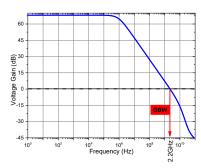

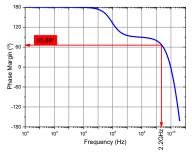

The VFET-based OTA design shows a high voltage gain of 44 dB, indicating efficient signal amplification. The gain-bandwidth product (GBW) of 986 MHz suggests the amplifier operates at high frequencies with good linearity. The phase margin of about 60 degrees ensures stability, reducing the risk of instability and oscillations. With a low power dissipation of 903  $\mu W$ , the circuit is efficient for low-power applications without compromising performance. These characteristics demonstrate the circuit's effectiveness in amplification, frequency response, and stability. Figure 5 presents the design results.

This work highlights the potential of VFETs in low-power and high-performance analog circuits. The VFET-based two-stage OTA design achieves a 44 dB voltage gain, 986 MHz GBW, and low power dissipation of 903µW, making it suitable for high-speed, low-power applications. The VFET's high intrinsic voltage gain, low output conductance, and high transconductance ensure efficient signal amplification and improved frequency response, demonstrating its promise for future analog circuit designs.

**Conclusions**

# Acknowledgments

The authors would like to thank CAPES, CNPq and FAPESP for the financial support and Imec for providing the samples used in this work.

- 1 Colinge, J. P. Silicon-On-Insulator Technology: Materials to VLSI. 3rd. Boston (MS): Kluwer Academic Publishers, 2004.

- 2 A. D. R. Ribeiro, V. C. P. Silva, J. A. Martino, A. Veloso, N. Horiguchi and P. G. D. Agopian, "Two-Stage Transconductance Operational Amplifier designed with VFET experimental data," 2024 38th Symposium on Microelectronics Technology and Devices (SBMicro).

- 3 E Simoen, A Veloso and P. Matagne, "Impact of the Channel Doping on the Low-Frequency Noise of Gate-All-Around Silicon Vertical Nanowire pMOSFETs", Solid-State Electronics, pp. 108576, 2023.

- 4 E Simoen, A Veloso and P. Matagne, "Impact of the Channel Doping on the Low-Frequency Noise of Gate-All-Around Silicon Vertical Nanowire pMOSFETs", Solid-State Electronics, pp. 108576, 2023.

- 5 Adel S. Sedra and Kenneth C. Smith, "MOS Field-Effect Transistors (MOSFETs)" in Microelectronic Circuits, Oxford University Press, vol. Chapter 4, 2014.

# A multi-phased clock TDC of 500 MHz at 62.5 ps developed in Cyclone-V FPGA

W. R. Melo<sup>1,2</sup>, J. A. Diniz<sup>1</sup>, E. B. Lima<sup>2</sup>, V. J. S. Oliveira<sup>3</sup> and S. Finco<sup>2</sup>

<sup>1</sup> Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas - FEEC UNICAMP

<sup>2</sup> Centro de Tecnologia da Informação Renato Archer – CTI

<sup>3</sup> Universidade do Estado de Mato Grosso - UNEMAT

E-mail: wellington.melo@cti.gov.br

### 1. Abstract

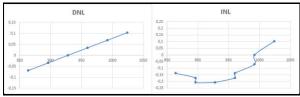

This work describes a Time-to-Digital Converter (TDC) based on a 32 multi-phased clock running at 500 MHz on a low-cost FPGA board. The TDC, named TDC32, has a theoretical resolution of 62.5 ps. Experimental tests using the Signal Tap environment showed a resolution of 61.55 ps, representing a 1.5% difference from the theoretical resolution. The main contribution of the TDC32 is its high linearity, with Differential Non-Linearity (DNL) ranging from +0.10 to -0.07 and Integral Non-Linearity (INL) ranging from +0.10 to -0.14. This work achieves high-end results using a low-end FPGA.

## 2. Introduction

Time-to-digital Converters (TDCs) are essential components in systems that measure time intervals with high precision. The counter, synchronized by a clock, forms the core of direct time measurements, with the clock's frequency defining the system's resolution and precision [1].

Recent technological advancements have driven increased research into TDCs, with applications spanning autonomous vehicles, particle counting, and topology verification [1, 5]. TDCs measure the time difference between an emitted and a reflected signal with high precision. The primary performance parameters are resolution, range, and linearity. Further insights can be found in references [1-8].

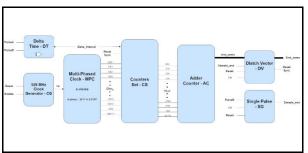

The proposed architecture is designed in a flexible and generic HDL language, ensuring portability across different technologies. The design focuses on RTL synthesis, particularly the technology map post-fitting. Figure 1 illustrates the block diagram of the 32 multiphased clocks, designated TDC32.

Fig.1. Block diagram of 32 multi-phased 500Mhz Clocks -

## 3. Simulation and experimental results

## A. Architecture, design, and simulation

The TDC consists of seven modular blocks, three of which are scalable to increase the number of phases. The DT block uses XOR logic to measure the interval between two signal events. The CG block generates the 500 MHz clock, while the MPC block generates 32 multiphased clock signals. The CS block counts each signal independently, and the AC block sums up the results. The SG block samples the results and resets the system synchronously, while the DV block stores the results in memory. Figure 2. illustrates the ModelSim - Intel FPGA Starter Edition 2020.1 simulation, part of Quartus Prime Lite 20.1.1.

Fig.2. Simulation of 32 multi-phased 500Mhz Clocks.

Figure 3. illustrates the simulation with a resolution of 62.5 ps sampled by the DV module.

Fig.3. Resolution of 62.5 ps and the result sampled by the DV module.

## B. Environment Testing

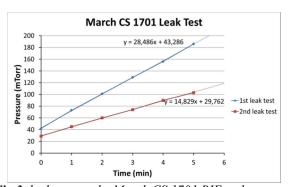

Experimental tests were conducted using the Signal Tap Logic Analyzer, an internal signal analysis and debugging tool from Quartus Prime. Signal Tap operates in real hardware, capturing waveforms of logic signals within the design. Figure 4 shows the output signals from the Signal Tap analysis, revealing a total count of 926 over a 57 ns interval, close to the theoretical 912, with a 1.5% deviation.

Fig. 4. Signal Tap Logic Analyzer with the design in real hardware Cyclone V (clocks and counter sum).

## C. Experimental results and discussions

The experimental resolution was measured at 61.55 ps, a 1.5% deviation from the theoretical 62.5 ps. Linearity tests with 64 samples across 11-time intervals yielded DNL values between +0.10 and -0.07 and INL values between +0.10 and -0.14, as illustrated in Figure 5.

Fig. 5. TDC32 linearity expressed in DNL and INL.

Table I compares the proposed TDC32 with a previous design by Mattada et al. [4], highlighting the superior linearity achieved on a low-cost FPGA platform.

TABLE I. COMPARATIVE TABLE

| Ref. No.  | No. of<br>Phases | Freq. (MHz) | Res.<br>(ps) | DNL            | INL            | FPGA<br>Platform  |

|-----------|------------------|-------------|--------------|----------------|----------------|-------------------|

| [4]       | 32               | 500         | 62.5         | +1 to -0.8     | +0.69 to -0.87 | Virtex 5 (2022)   |

| [4]       | 16               | 700         | 89,9         | +0.44 to -0.87 | +0.44 to -0.82 | Kintex7<br>(2016) |

| This Work | 32               | 500         | 62.5         | +0,10 to -0,07 | +0,10 to -0,14 | Cyclone 5 (2025)  |

Concerning utilising the available devices, TDC32 employs less than 1% of the total Adaptive Logic Module (ALM). The generic HDL description in this work does not include any property modules, such as PLLs. However, Mattada et al. [4] (2022) utilise four PLLs in

their design, which account for 66% of the devices available on Virtex. 5. The strategy of not using any property module is to ensure portability across different technologies and FPGAs.

## 4. Conclusions and Future Works

This work demonstrates that high-end performance can be achieved using a low-cost FPGA. The TDC32's modular design allows scalability to increase the number of phases, thereby improving resolution while maintaining linearity. By modifying the number of phases in just three blocks (MPC, CS, and AC) and adjusting the corresponding delay times for the target frequency, it is possible to achieve the desired phase variation. Future work will explore the implementation of TDC64 and TDC128 architectures.

## Acknowledgements

The authors acknowledge their respective institutions and the National Council for Scientific and Technological Development (CNPq) under the CPSAE Project (Grant No. 422360/2023-6) for supporting this research.

- [1] Mattawa MP, Guhilot H. Time-to-digital converters—A comprehensive review. Int J Circ Theor Appl. 2021;49:778–800. https://doi.org/10.1002/cta.2936.

- [2] Yu Wang, Wujun Xie, Haochang Chen, David Day-Uei Li High-resolution time-to-digital converters (TDCs) with a bidirectional encoder, Measurement 206 (2023) 112258 https://doi.org/10.1016/j.measurement.2022.112258.

- [3] P. Napolitano, A. Moschitta, P. Carbone A Survey on Time Interval Measurement Techniques and Testing Methods IEEE 978-1-4244-2833-5/10 2010.

- [4] Mahantesh Mattada, Hansraj Guhilot "62.5 ps LSB resolution multi-phase clock Time to Digital Converter (TDC) implemented on FPGA" Journal of King Saud University Engineering Sciences 34 (2022) 418–424 https://doi.org/10.1016/j.jksues.2021.01.007.

- [5] Szyduczynski, Jakub, Dariusz Koscielnik, and Marek Miskowicz. "Time-to-digital Conversion Techniques: A Survey of Recent Developments." Measurement: Journal of the International Measurement Confederation 214 (2023): Journal of the International Measurement Confederation, 2023, Vol.214. Web.

- [6] W. R. Melo, J.A. Diniz, S. Finco, M. C. Carlos and V. J. S. Oliveira A multi-phased ring oscillator TDC, designed in HDL language, applied to a low-cost FPGA XVII Workshop on Semiconductors and Micro & Nano Technology SEMINATEC 2023 March 29th to 31st.

- [7] W. R. Melo, J. A. Diniz, A. C. C. Telles, E. B. Lima, V. J. S. Oliveira and S. Finco "An Internal Clock Family into Low-Cost Cyclone V FPGA for High-Range and High-Resolution TDCs" XVIII Workshop on Semiconductors and Micro & Nano Technology SEMINATEC 2024 April 18th to 19th, 2024.

- [8] W. R. Melo, J. A. Diniz, V. J. S. Oliveira and S. Finco "Multi-Phased Oscillator for TDC applications implemented in low-cost FPGA" Workshop on Circuits and System Design WCAS2024 Chip on the Cliffs 2024– September 2nd to 6th, 2024.

# DESIGN AND OPTIMIZATION OF A CMOS POWER AMPLIFIER FOR 6 GHz APPLICATIONS

P. V. F. Silva, and S. P. Gimenez <sup>1</sup>

<sup>1</sup> FEI University Center

paulovfs@fei.edu.br, sgimenez@fei.edu.br

## 1. Abstract

This work presents the design and optimization of a Radio Frequency Power Amplifier (RFPA) for applications in fifth-generation (5G) networks operating at 6 GHz. The amplifier was developed using 65 nm Complementary Metal-Oxide-Semiconductor (CMOS) integrated circuit (ICs) technology, aiming for efficiency and high-frequency performance. The results indicate a forward transmission coefficient (S21) of 15.2 dB, an input reflection coefficient (S<sub>11</sub>) of -12.4 dB, an output reflection coefficient (S22) of -11.9 dB, and a reverse transmission coefficient (S<sub>12</sub>) of -20.4 dB. These parameters demonstrate the feasibility of the amplifier for wireless communication applications, highlighting its robustness and electrical performance under hard operating conditions. The computational "iMTGSPICE" was used to design and optimize CMOS ICs based on the optimization heuristic algorithms of Artificial Intelligence (AI), integrated with the designers' expertise (Human intelligence, IH), of a robust way (Corner and Monte Carlo analyses). Thus, the efficient operation of the RFPA in high-frequency applications was ensured, consolidating its relevance for 5G networks in the 6 GHz band [1] [2].

# 2. Introduction

The demand for efficient wireless communication systems, such as 5G and the Internet of Things (IoT), drives the need for high electrical performance RFPAs. The CMOS IC technology offers miniaturization and energy efficiency advantages but faces challenges in RF CMOS IC applications due to process variations and nonlinearities. This work addresses these challenges by proposing a Class-F<sup>-1</sup> PA optimized and robust for 6 GHz using a hybrid AI-human approach. The design focuses on achieving high voltage gain, impedance matching, and robustness against manufacturing process uncertainties [1] [2].

# 3. Methodology

The project was developed in four main steps. The first stage involved the study of the reference [2], which was used as a reference to define the RFPA architecture.

In the second step (Project 1), the electrical behavior of the RFPA from the article was analyzed using 65 nm CMOS ICs technology to validate the simulated and experimental results. Testbench circuits were generated in SpiceOpus to extract the figures of merits (FoMs) values, which were nominal and did not include the

robustness analyses (Corner and Monte Carlo). The analyses were performed manually.

The third step (Project 2) considers the RFPA specifications of [2], considering  $\pm 10\%$  variations of the component values defined in [2] too. Using iMTGSPICE, robustness analyses were conducted to evaluate the circuit's electrical performance under different process, voltage, and temperature (PVT) conditions.

In the fourth step (Project 3), the specifications were defined based on the FoMs defined by [2], and the input variables (MOSFET dimension, components values, bias conditions, etc.) were adjusted to iMTGSPICE obtain the best robust solutions.

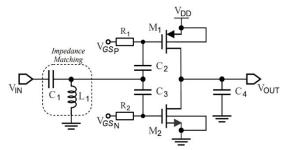

## 4. RFPA topology

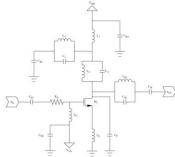

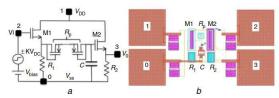

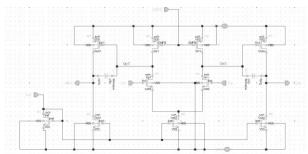

Fig. 1 illustrates the schematic diagram of the RFPA.

Fig. 1. RFPA Topology [2].

The RFPA proposed in [2] is of the Inverse Class-F type (Class-F<sup>-1</sup>), designed to operate at a frequency (f) of 6 GHz and manufactured using TSMC's (Taiwan Semiconductor Manufacturing Company) 65 nm CMOS IC technology. The electronic circuit of the RFPA designed in [2] is illustrated in Fig. 1.

Where n<sub>in</sub> and n<sub>out</sub> are, respectively, the input and output nodes of the circuit, C<sub>1</sub>, C<sub>2</sub>, C<sub>B1</sub>, C<sub>B2</sub>, C<sub>B3</sub>, C<sub>B4</sub>, C<sub>R1</sub>, and C<sub>M</sub> are the capacitors designed for the RFPA circuit,  $L_G$ ,  $L_S$ ,  $L_1$ ,  $L_2$ ,  $L_3$ , and  $L_{R1}$  are the inductors designed for the RFPA circuit, R<sub>G</sub> is the input resistor of the circuit, M<sub>1</sub> is the nMOSFET, and C<sub>P</sub> is the parasitic capacitor (which expresses the parasitic capacitance) of the manufacturing process [2]. The circuit uses an architecture with a single nMOSFET, implemented with 6 unitary nMOSFETs connected in parallel, all of which have the same number of fingers [N<sub>fingers</sub>]. In this research project described in reference [2], each unitary transistor contains 32 fingers, resulting in an equivalent nMOSFET with 192 fingers (M<sub>1</sub>). The RFPA is biased with a voltage source (V<sub>DD</sub>) of 1.1 V and a gate voltage source (V<sub>GG</sub>) of 480 mV. The architecture includes a resistor (R<sub>G</sub>) and an

inductor (L<sub>S</sub>) connected to the transistor's Gate for amplifier stabilization [2]. The amplifier implements a harmonic control network at the drain of the nMOSFET, shaping the voltage and current waveforms at the drain to minimize their overlap and thus increase efficiency. The circuit takes advantage of the parasitic capacitor (C<sub>P</sub>) inherent to the technology in the harmonic control network [2]. Regarding the first harmonic signals (6 GHz), the parallel-tank circuit formed by inductor L<sub>3</sub> and capacitor C<sub>1</sub> (T<sub>P(L3,C1)</sub>) resonates at 6 GHz, creating an open circuit and not interfering with the circuit. The parallel-tank circuit formed by inductor L<sub>2</sub> and capacitor C<sub>2</sub> (T<sub>P(L2,C2)</sub>) acts as an inductor at this frequency and, along with inductor L<sub>1</sub>, cancels out the effects of the parasitic capacitor (C<sub>P</sub>) [2]. For second harmonic signals (12 GHz), T<sub>P(L2,C2)</sub> continues to act as an inductor, functioning to cancel out the effects of C<sub>P</sub>. T<sub>P(L3,C1)</sub> behaves as a capacitor, creating a low-impedance path to the circuit's ground (reference node), eliminating the undesirable effects of 12 GHz signals [2]. At the third harmonic (18 GHz), T<sub>P(L2,C2)</sub> behaves as a capacitor and, combined with inductor L<sub>1</sub>, forms a series-tank circuit, creating a short circuit to the ground. T<sub>P(L3,C1)</sub> also acts as a capacitor at this frequency, diverting third harmonic signals to the ground [2]. The inductor  $L_{R1}$ , capacitor  $C_{R1}$ , and capacitor C<sub>M</sub> combined at the RFPA output serve two purposes. The first purpose is impedance matching, where the parallel-tank circuit formed by inductor L<sub>R1</sub> and capacitor C<sub>R1</sub> (T<sub>P(LR1,CR1)</sub>) (which behaves as an inductor at frequencies lower than 18 GHz) and capacitor C<sub>M</sub> are used to ensure maximum electrical power transfer to the load and avoid reflections. The second purpose of T<sub>P(LR1,CR1)</sub> is to create an open circuit for second harmonic signals [2]. The capacitors C<sub>B2</sub> and C<sub>B4</sub> are decoupling capacitors, capacitor C<sub>B1</sub> is a coupling capacitor, C<sub>B3</sub> functions as a decoupling capacitor and influences the harmonic control network, and L<sub>G</sub> is an inductor in the RFPA input network [2].

# 5. Experimental Results

Working with the iMTGSPICE, the authors present the best robust solution for Project 3, regarding the S parameters (Table I).

**Table I.** S parameters reported in [2] and Project 3 (robust solution).

| FoM             | Reported values in [2] (it is not a robust solution) | Value in this work (robust solution) |

|-----------------|------------------------------------------------------|--------------------------------------|

| S <sub>21</sub> | 15 dB                                                | 15.2 dB                              |

| S <sub>11</sub> | -28 dB                                               | -12.4 dB                             |

| S <sub>12</sub> | -33 dB                                               | -20.4 dB                             |

| S <sub>22</sub> | -20 dB                                               | -11.9 dB                             |

| ηРАЕ            | 52%                                                  | 46.2%                                |

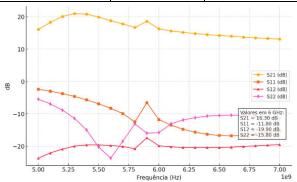

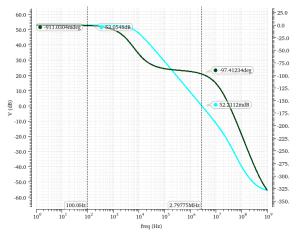

Observe that to obtain a robust solution for Project 3, it was impossible to reach all specifications reported in [2], regarding a 65 nm CMOS ICs technology and a wide range of temperatures (0-70°C) (not reported in [2]). The input variables' values obtained for Project 3 are presented in Table II, and Fig. 2 illustrates the S parameters as a function of the frequency obtained by iMTGSPICE for Project 3.

Table II. Input variables results obtained for iMTGSPICE.

| Variable                               | [2] Value | Project 3 |

|----------------------------------------|-----------|-----------|

| $C_1$                                  | 3 pF      | 2.82 pF   |

| $C_2$                                  | 255 fF    | 230 fF    |

| $C_{B1}$                               | 5 pF      | 0.45 pF   |

| $C_{B2}$                               | 5 pF      | 5 pF      |

| C <sub>B3</sub>                        | 10 pF     | 0.075 pF  |

| $C_{B4}$                               | 5 pF      | 5 pF      |

| См                                     | 4 pF      | 0.25 pF   |

| $C_{R1}$                               | 202 fF    | 202 fF    |

| $L_1$                                  | 2.42 nH   | 1 nH      |

| $L_2$                                  | 351 pH    | 316 pH    |

| L <sub>3</sub>                         | 234 pH    | 253 pH    |

| L <sub>G</sub>                         | 631 pH    | 1 nH      |

| $L_{R1}$                               | 874 pH    | 961 pH    |

| Ls                                     | 88 pH     | 15 pH     |

| $R_{\mathrm{G}}$                       | 5 Ω       | 6 Ω       |

| Nfingers                               | 32        | 32        |

| nMOSFETs parallel                      | 6         | 1         |

| N <sub>fingers</sub> (M <sub>1</sub> ) | 192       | 32        |

| W (finger)                             | 2 um      | 6 um      |

| L                                      | 0.06 um   | 0.07 um   |

| $V_{GG}$                               | 0.480 V   | 0.75 V    |

| $V_{\mathrm{DD}}$                      | 1.1 V     | 0.95 V    |

Fig. 2. RFPA S parameters as a function of the f (Project 3).

We observe that the RFPA is able to reach a robust solution for 6 GHz and, consequently, the needs of the 5G CMOS ICs applications operating in a wide temperature range (0-70 °C).

# 6. Conclusions

The robust radiofrequency power amplifier (Class-F<sup>-1</sup>) was designed and optimized robustly (Corner and Monte Carlo analysis) using the iMTGSPICE for the 5G (6 GHz) wireless network applications to operate in a wide range of temperatures (0-70 °C).

# Acknowledgments

Our thanks to SBMICRO, FEI, and INCT Namitec.

- [1] HARA, A. T. Amplificador de potência RF CMOS banda larga para comunicação 5G sub-6GHz, 2021.

- [2] Ali, S. M. A.; Hasan, S. M. R. A 6 GHz Integrated High-Efficiency Class-F<sup>-1</sup> Power Amplifier in 65 nm CMOS Achieving 47.8% Peak PAE. Electronics. Basel, v. 10, n. 2450, out. 2021.

- [3] KAZIMIERCZUK, M. K. *RF Power Amplifiers*. 2. ed. Hoboken: John Wiley & Sons, 2015.

# Development of low-noise amplifiers for the detection of a few photons using silicon photomultipliers

R. S. Soares<sup>1</sup>, L. T. Manera<sup>1</sup> and M.V. Puydinger dos Santos<sup>1</sup>

<sup>1</sup> Electrical and Computer Engineering Faculty (FEEC) - State University of Campinas – UNICAMP e-mail: <u>r261649@dac.unicamp.br</u>

### 1. Abstract

Silicon photomultipliers (SiPMs) are solid-state components that produce electrical pulses in response to the absorption of photons and are widely used as optical sensors in detectors of particles and cosmic rays [1].

In general, using SiPMs saves space, energy and costs compared to the traditional photomultiplier tube (PMTs) [2], in addition to be CMOS-compatible and produced using silicon technology. With this in mind, this work proposes the development of a low-noise amplifier dedicated to low signals produced by a reduced number of photons (of the order of 10<sup>3</sup>), which were generated in a home-made environment.

### 2. Introduction

One of the technological advances brought about by this research is the proposal to make SiPMs viable alternatives to photomultiplier tubes (PMTs). The aim is to improve the amplification of signals obtained through light detection and to make the infrastructure and data collection more straightforward and accurate. It turns out that SiPMs require less sophisticated electronics and, hence, less power consumption, which reduces the cost of the infrastructure needed to produce the device, besides allowing for better noise control for more sensitive applications.

One applied research project already underway and complementary to this work is in the area of particle physics (developed at IFGW/UNICAMP) [1][3]. This group researches the development of new theories of physics through the detection of neutrinos indirectly by trapping scintillated light (ARAPUCA experiment) [3], which can be detected by SiPMs. The origins of the neutrinos studied are both cosmic and from a particle accelerator (DUNE experiment) [4].

# 3. Results and Discussion

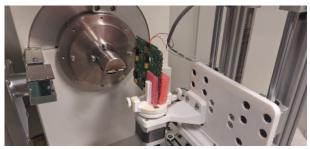

Preliminary results show that the experimental setup developed is capable of generate and amplify pulses of a few photons, of the order of  $6 \times 10^3$  photons/pulse, making the signal measurable in conventional electronics systems.

# A. Environment development and photon density control

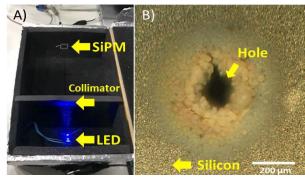

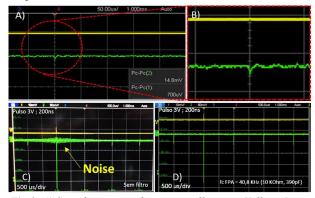

Considering the experiments with variations of solid angle, color, distance, inclination, collimator, voltage, and pulse time with the LED power, plus the efficiency characteristics of the SiPM ( $\eta E$ ), it is possible to estimate

the photons that reach the detector from the pulses generated by the LED, to calculate a better correlation between the photons that are absorbed by the photomultiplier and its generated signal, and subsequently the amplification. The low photon chamber (Fig. 1A) consists of a LED positioned in front of the SiPM and a collimator in between. This collimator consists of a silicon piece with a 200 µm-wide hole (Fig. 1B) drawn using a laser milling.

Fig. 1. A) Box of test environment. B) 200 µm-wide aperture collimator produced by laser milling to reduce the photon flux.

## B. Photon density estimation

The LED used in the experiments has  $\lambda = 460$  nm wavelength. Therefore, we calculate the corresponding energy:

$$E_f(\lambda) = \frac{h.c}{\lambda} \cong 4.32 \times 10^{-21} J \tag{1}$$

Considering the LED overall power of 120 mW and a pulse width of 30 ns, the energy generated by the LED at each pulse can be calculated by:

$$E_{t LED} = P_{LED} \cdot \Delta t = 3.6 \times 10^{-9} J/pulse$$

(2)

The number of emitted photons  $(N_e)$  could be calculated as follows:

$$N_e = \frac{E_{t\,LED}}{E_f} = 8.33 \times 10^{11} \, photons/pulse$$

(3)

Here, we consider as a first approximation that the LED power produces the spectral distribution restricted to the peak at 460 nm. Moreover, considering the variation of LED and collimation reduction factors, it is possible to calculate how many of these photons are being absorbed by the SiPM. These are reduction by: angle of the LED ( $\eta$ I), reduction of the solid angle by collimator ( $\eta$ C) and the reduction by SiPM efficiency ( $\eta$ E), as shown in Table I. Therefore, the number of photons absorbed by SiPM ( $N_a$ ) follows as:

$$N_a = N_e \cdot \eta I \cdot \eta C \cdot \eta E = 6.67 \times 10^3 \ photons$$

(4)

**Table I.** Types of reductions in the number of photons.

| Number of             | Reduction Coefficient |            |            |  |

|-----------------------|-----------------------|------------|------------|--|

| emitted photons       | Inclination           | Collimator | Efficiency |  |

| $(N_e)$ in 30 ns      | 45° (ηΙ)              | (ηC)       | (ηE)       |  |

| $8,33 \times 10^{11}$ | 1%                    | 0.0002%    | 40%        |  |

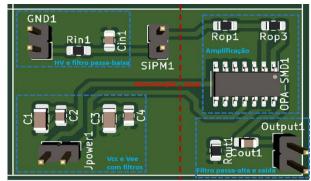

#### C. Noise reduction

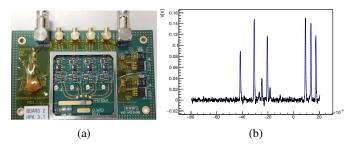

To reduce the noise levels we have included passive filters (low-pass to input of SiPM and high-pass to output of amplification), electromagnetic isolation with case grounding, integrated circuits (IC) with low noise inputs and high voltage (HV) choices, as the use of SMD components and PCB framework optimization (Fig. 2). The cutoff frequencies of the low- and high-pass filters are presented in Table II. Through comparisons of the curves obtained by the oscilloscope, it is possible to observe the differences in the noise level and signal stability during the light pulse conversion into electrical pulse.

Fig. 2. Design of amplification PCB using SMD component and separation in layout.

Table II. Passive filters used in the project.

| Those 110 I dissive fitters disease in the project. |                    |                     |  |  |  |  |

|-----------------------------------------------------|--------------------|---------------------|--|--|--|--|

| Passive filters                                     | Low-pass<br>filter | High-pass<br>filter |  |  |  |  |

| Cut-off frequency                                   | 159,1 Hz           | 40,8 KHz            |  |  |  |  |

## D. Amplification of electrical signals

As work developed, it was possible to build a first prototype to validate the study and a well-founded correlation between photons and the electrical signal generated at the amplifier's output.

With the improvements in obtaining the results, the gain value was gradually increased until it reached -47  $(R_1 = 1 \ k\Omega; R_2 = 47 \ k\Omega)$ , as shown in Fig. 3, evolving from previous tests with gains of G = -2, G = -10 and G = -47, choosing to remain at -47, and not increasing, as the experiments showed good signal conversion with relatively high signal-to-noise ratio, thus proving its concept and good functionality. In this sense, the focus of the work was not only to increase the gain, but also to study other aspects, such as the challenge associated with the variable gain about the calculated value, filter losses, differences in the values of the triggers/thresholds and the observation of the characteristic central peak that might be related to some sort of intrinsic noise from the power

supply. These characteristics are essential elements for a complete understanding and characterization of the amplifier circuit.

Fig. 3. A) Signal gain seen from an oscilloscope. Yellow: Input. Green: Output. B)Zoom of the amplified signal, also shown C) without filter and D) with a filter setup.

## 4. Conclusions

In summary, the current results indicate significant progress in the development of an SiPM-based amplifier for a small number of photons. With this experiment, we mimic the low amount of photons produced by noninteracting particles such as neutrinos, which can be detected indirectly by the small number of photons produced when interacting with a material medium. The environmental chamber fabricated shows a considerable reduction in the number of photons, as well as allowing SiPMs to be tested more accurately at low light intensities. The amplified electrical signal demonstrates the quality of the circuit proposed for amplifying the electrical signal from the light pulses. Our fabricated setup can be ultimately used to emulate a system with low amount of photons and, therefore, allows for the implementation of powerful amplification circuits capable of detecting such a small optical signal by SiPMs.

## Acknowledgments

The authors thank Prof. Ana Amélia Machado and Prof. Ettore Segreto for the experimental support, as well as the Federal University of ABC for the experimental facility. This work was financially supported CNPq (grant #310021/2021-9 and #406193/2022-3).

- [1] A. A. Machado, A. C. Fauth, V. do Lago Pimentel, and E. Segreto, "C-Arapuca: An Innovative Device for Detecting Cherenkov Radiation," Brazilian J. Phys., vol. 54, no. 6, pp. 3–7, 2024, doi: 10.1007/s13538-024-01616-6.

- [2] Hamamatsu photonics, "What is MPPC (SiPM)?" [Online].Available:https://www.hamamatsu.com/jp/en/product/optical-sensors/mppc/what is mppc

- [3] H. da Motta et al., "ARAPUCA light trap for large liquid argon time projection chambers," Proc. Sci., vol. 295, no. January, 2017, doi: 10.22323/1.295.0153.

- [4] Fermi National Accelerator Laboratory, "DUNE: An International Experiment for Neutrino Aiming for groundbreaking discoveries." [Online]. Available: https://www.dunescience.org/

# Metallized Substrate Technologies – A Cost-effective Approach for RF Circuits and Photonic Packaging

C. A. Finardi<sup>1</sup>, A. Flacker<sup>2</sup>, F. S. Correra<sup>3</sup>, J. E. C. Mattar<sup>2</sup>, C. R. Biazoli<sup>4</sup>, R. C. Teixeira<sup>2</sup>, H. E. Hernández-Figueroa<sup>1</sup>, R. R. Panepucci<sup>2</sup>

<sup>1</sup>FEEC/Unicamp, Campinas, Brazil

<sup>2</sup>CTI Renato Archer, Campinas, Brazil

<sup>3</sup>I aboratório Microeletrônica/FPUSP, São Paulo, Brazil

<sup>3</sup>Laboratório Microeletrônica/EPUSP, São Paulo, Brazil <sup>4</sup>Rosa dos Ventos Automação. Campinas, Brazil e-mail: celio.finardi@yahoo.com.br

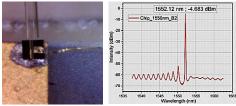

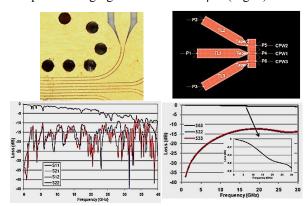

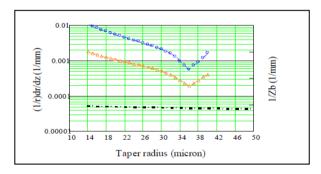

### 1. Abstract

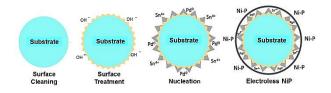

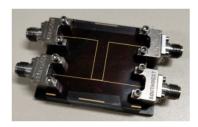

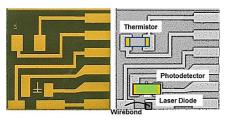

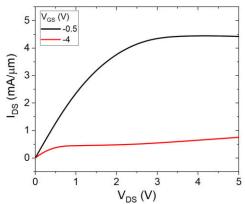

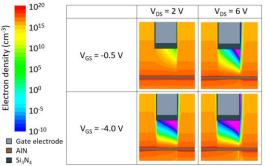

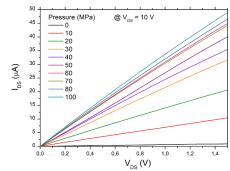

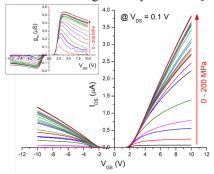

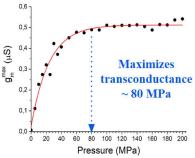

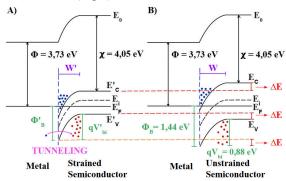

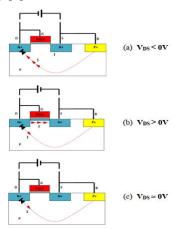

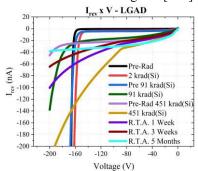

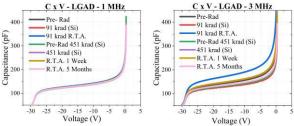

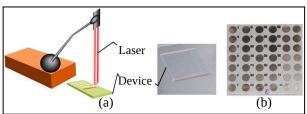

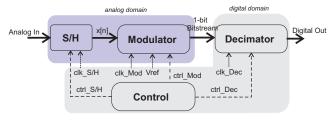

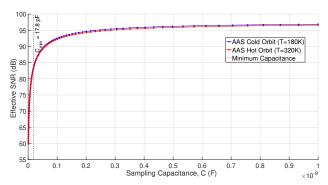

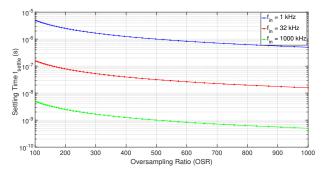

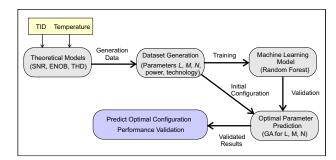

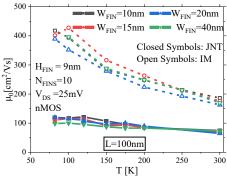

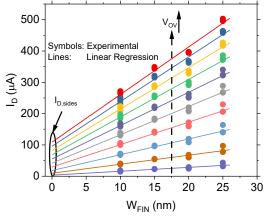

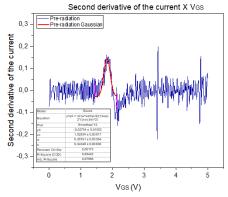

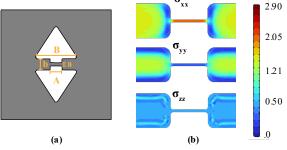

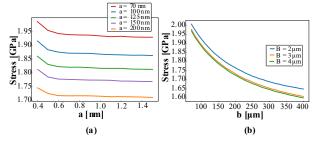

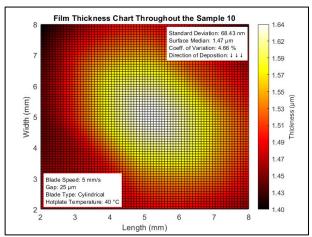

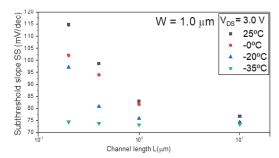

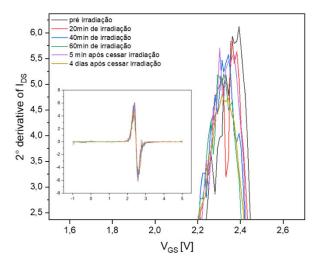

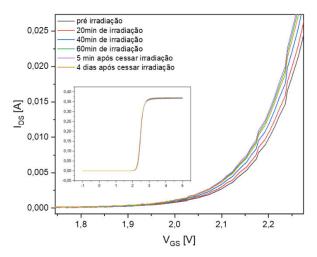

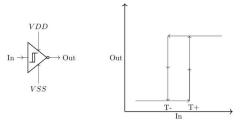

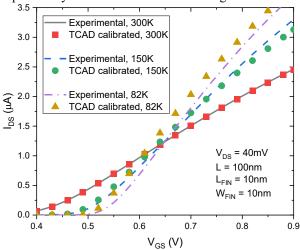

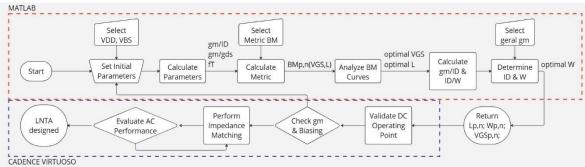

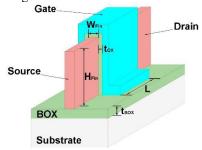

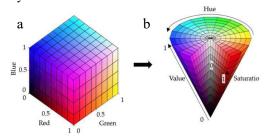

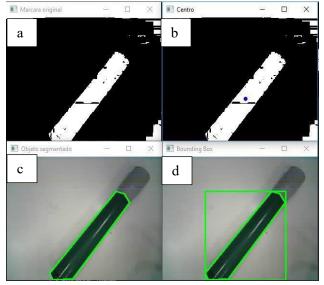

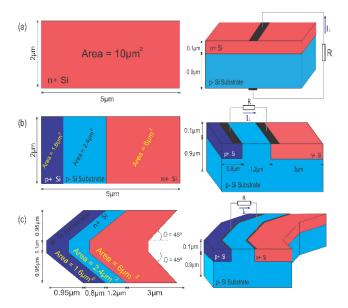

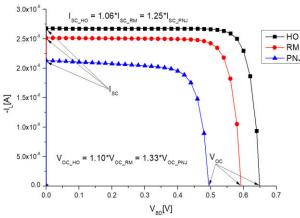

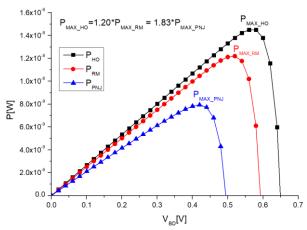

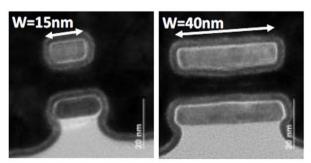

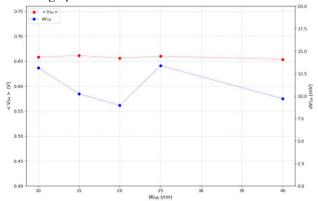

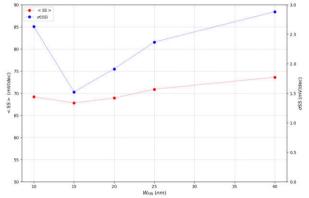

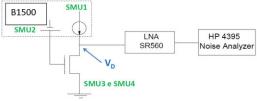

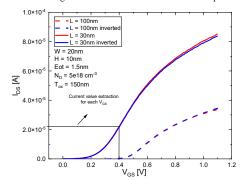

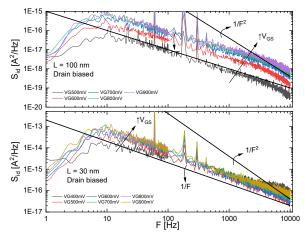

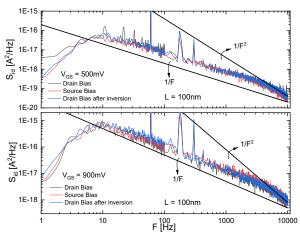

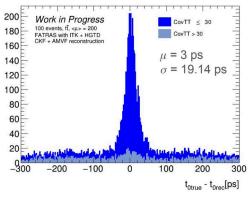

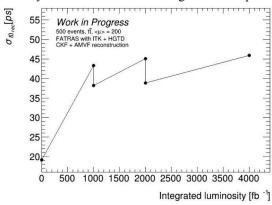

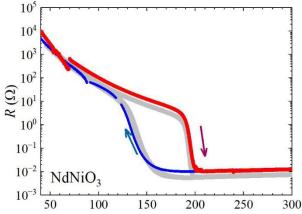

With technological advancements across various sectors, metallized substrates play a crucial role in enabling increasingly compact innovations with multiple functionalities.