# CARACTERIZAÇÃO ELÉTRICA DA ASSOCIAÇÃO SÉRIE ASSIMÉTRICA DE TRANSISTORES FD SOI MOS

Gabriel Antonio Bueno Moreira<sup>1</sup>, Michelly de Souza Engenharia Elétrica, Centro Universitário da FEI a.gabrielbueno@fei.edu.br, michelly@fei.edu.br

**Resumo:** Este artigo apresenta resultados experimentais da caracterização elétrica da associação série assimétrica de transistores FD SOI. É mostrado que a transcondutância tende aos valores dos transistores isolados com comprimento igual a  $L_{\rm S}$ . A condutância de saída sofre redução significativa quando  $L_{\rm S}$  é muito menor que  $L_{\rm D}$  e quando  $V_{\rm DS}$  é muito maior que  $V_{\rm GT}$ . Além disso, a estrutura assimétrica proporciona aumento de até 26dB, quando comparada aos transistores isolados, além de permitir a redução de comprimento, sem degradação de  $A_{\rm V}$ .

# 1. Introdução

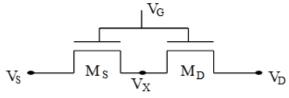

Com o intuito de minimizar os efeitos decorrentes do elevado campo elétrico na região de dreno dos transistores da tecnologia FD (fully-depleted) SOI (Silicon-On-Insulator) [1], algumas estruturas alternativas têm sido exploradas, visando a obtenção de circuitos analógicos de alto desempenho. Uma das soluções mais largamente empregadas para reduzir-se a condutância de saída de transistores MOS é a utilização de uma alteração da estrutura self-cascode chamada de associação de transistores SOI, apresentada na Figura 1, na qual os transistores são associados em série com suas portas curto-circuitadas, operando como um único transistor [2].

Figura 1 - Representação da associação série assimétrica.

Com o objetivo de aumentar a tensão de ruptura e reduzir g<sub>D</sub>, foi proposta a associação assimétrica de transistores, na qual os dois transistores apresentam diferentes concentrações de dopantes na região do canal [3]. Assim, a associação apresenta um transistor com concentração de dopantes mantida em valores habitualmente utilizados em transistores FDSOI convencionais, do lado da fonte (M<sub>S</sub>), a qual fixa o valor da tensão de limiar, e a outra com concentração reduzida, junto ao dreno (M<sub>D</sub>), diminuindo o campo elétrico nesta região. Este projeto tem como objetivo estudar o desempenho elétrico da associação série assimétrica de transistores FD SOI com diferentes comprimentos de canal.

# 2. Metodologia

Foram caracterizados eletricamente transistores FDSOI fabricados na Université catholique de Louvain - UCLouvain (Bélgica) em modo *self-cascode*, com comprimentos de canal L<sub>S</sub> e L<sub>D</sub> variando entre 0,75 e 10 um e W = 20 um. Os transistores apresentam espessura de camada de Si, óxido de porta e óxido enterrado de 80nm, 31nm e 390nm respectivamente. Foram usados transistores com duas concentrações de dopantes: 6x10<sup>16</sup> cm<sup>-3</sup> e 1x10<sup>15</sup> cm<sup>-3</sup>. Assim, no total, foram extraídas curvas para 100 combinações de M<sub>S</sub> e M<sub>D</sub> para as associações e mais 10 para cada série de transistores isolados (baixa e alta concentração de dopantes), totalizando 120 transistores. A partir das curvas de correntes medidas destas combinações, foram extraídos parâmetros como tensão de limiar transcondutância (g<sub>m</sub>), condutância de saída (g<sub>D</sub>) e ganho de tensão (A<sub>V</sub>).

Para cada combinação de transistores, foram levantados 3 tipos de curvas, sendo:

- a)  $I_{DS}$  x  $V_G$  com  $V_{DS}$  = 50mV para extração de  $V_{TH}$ , a partir do método da segunda derivada de  $I_{DS}$  x  $V_G$  [4].

- b)  $I_{DS}$  x  $V_G$  com  $V_{DS}$  = 500mV até 1,50V, com passo de 250mV, de onde foram extraídas as curvas de  $g_m$  x  $V_G$  através da equação 1.

$$g_m = dI_{DS}/dV_G \tag{1}$$

c)  $I_{DS}$  x  $V_{DS}$  para  $V_G$  entre 0V até 800 mV acima de  $V_{TH}$  ( $V_{GT} = V_G - V_{TH}$ , ou sobretensão de condução), com passo de 200 mV, de onde foram levantadas as curvas de  $g_D$  em função de  $V_{DS}$ , para cada valor de  $V_{GT}$  através da equação 2.

$$g_D = dI_{DS}/dV_{DS} \tag{2}$$

#### 3. Resultados

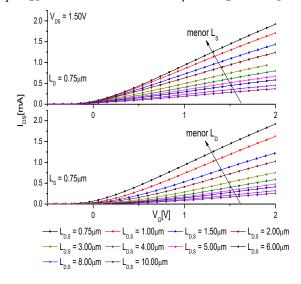

As curvas de  $I_{DS}$  em função de  $V_G$  para dois tipos de associação ( $L_D$  fixo e  $L_S$  variando e vice-versa) para  $V_{DS}$ =1,5V, estão apresentadas na Fig. 2. Foi observado que  $I_{DS}$  aumenta tanto com a redução de  $L_D$  como  $L_S$ .

Figura 2 - Curvas  $I_{DS}$  x  $V_G$  para diferentes  $L_D$  e  $L_S$  com  $V_{DS} = 1,5V.$

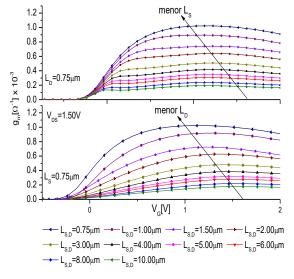

A partir da derivada das correntes de dreno em função da tensão de porta, foram obtidas as curvas de transcondutância apresentadas na Fig. 3, para associações com  $L_D$  fixo e  $L_S$  variando e vice-versa, com tensão de dreno  $V_{DS} = 1,5V$ . Observando as curvas, podemos notar que assim como para a corrente de dreno, a transcondutância é inversamente proporcional aos comprimentos de canal  $L_S$  e  $L_D$ .

Devido à baixa resistência apresentada pelo transistor  $M_D$ , que apresenta tensão de limiar negativa, maiores valores de tensão atingem o dreno de  $M_S (V_X)$ , resultando em maior corrente e transcondutância.

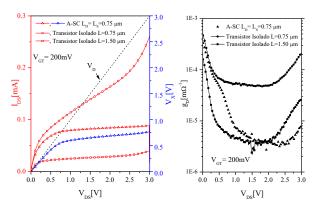

A Fig. 4 apresenta as curvas de  $I_{DS}$  e tensão no nó intermediário  $(V_X)$ , em função de  $V_{DS}$ , e a Fig. 5 as curvas de  $g_D$  em função de  $V_{DS}$ , extraídas com  $V_{GT} = 200 \text{mV}$ . Comparando os transistores isolados, com as associações, nota-se que a associação apresenta grande redução na condutância de saída. Essa redução ocorre em função da tensão  $V_X$  da associação. A tensão  $V_X$  se mantém igual a  $V_{DS}$ , até o momento em que ambos transistores entram em saturação, onde, a partir desse ponto,  $M_D$  absorve o aumento de  $V_{DS}$ , diminuindo  $g_D$ , que se torna próximo à condutância de saída do transistor isolado com  $L=1,50~\mu m$ , porém apresentando maior nível de corrente.

Figura 3 - Curvas  $g_m$  x  $V_G$  para  $L_D$  = 0,75  $\mu m$  e  $L_S$  variando e  $L_S$  = 0,75  $\mu m$  e  $L_D$  variando ( $V_{DS}$ =1,5V).

Observando-se os valores de  $g_D$  para as diversas associações de  $L_S$  e  $L_D$  pôde-se observar que quanto menor é  $L_S$  em relação à  $L_D$ , menor é o valor de  $g_D$ , chegando a apresentar uma redução de até 93,05%, quando  $V_{DS}=1,50V$  e  $V_{GT}=0V$ .

A partir da relação  $g_{m}/g_{D}$ , foram calculados os valores do ganho de tensão  $(A_{V})$  para algumas das associações medidas. A maior diferença de ganho, encontrada entre a associação de menor e maior comprimento, foi de  $A_{V}=27,4$  dB, ocorrendo para  $V_{GT}=0V$ . Os maiores valores de  $A_{V}$  foram observados de associações com maiores comprimentos  $L_{S}$  e  $L_{D}$ . Entretanto, o uso da associação permite a redução das dimensões de L, sem degradação do ganho em comparação com transistores isolados. Por exemplo, a associação assimétrica com  $L_{D}=L_{S}=0,75$  µm, apresenta

um ganho  $A_V$ = 41,7dB que é maior do que o ganho do transistor isolado com baixa concentração de dopantes, com L=2  $\mu$ m ( $A_V$ = 35,93dB), vide Tabela 1.

Figuras 4 e 5 - Curvas I<sub>DS</sub> x V<sub>X</sub>(4) e g<sub>D</sub> x V<sub>DS</sub>(5) para assoc. assimétrica e transistor isolado.

| Associações         | AV[dB] |

|---------------------|--------|

| LD = LS = 0.75 μm   | 41.7   |

| LD = 2 µm (Isolado) | 35.93  |

Tabela 1 - Ganhos calculados para a associação assimétrica e transistor isolado.

### 4. Conclusões

Os resultados mostraram que as características analógicas do transistor assimétrico, são melhoradas pelos aumentos dos comprimentos de  $L_{\rm S}$  e  $L_{\rm D}$ . Selecionando o comprimento dos transistores associados, é possível reduzir significativamente o valor de  $g_{\rm D}$ . Em relação a  $g_{\rm m}$ , seus valores tenderam aos dos transistores isolados com comprimento igual a  $L_{\rm S}$ . Sendo assim, foi possível a obtenção de alto ganho para as associações comparado aos dispositivos isolados de L similar, chegando em até 26 dB de aumento na associação assimétrica, além de a associações permitirem a redução de L, sem causar degradação significativa de  $A_{\rm V}$ .

# 5. Referências

- [1] J.P, Colinge. Silicon-On-Insulator Technology: Materials to VLSI. 3rd Ed. Massachusetts: Kluwer Academic Publishers. 2004.

- [2] Galup-Montoro, C. et al., IEEE JSSC, v. 29, n. 9, p.1094-1101, 1994.

- [3] Souza, M. de Flandre, D., Pavanello, M. A. Asymmetric Self-Cascode Configuration to Improve the Analog Performance of SOI nMOS Transistors. Proc. of 2011 IEEE International SOI Conference, p. 1-2, 2011.

- [4] A. Ortiz-Conde et al. Revisiting MOSFET threshold voltage extraction methods Microelectronics Reliability, vol. 53, n. 1, pp 90-104, 2013.

# Agradecimentos

À instituição UCLouvain pela disponibilização do chip estudado.

Aluno de IC do Centro Universitário FEI. Projeto com vigência de 06/19 a 05/20.