# ESTUDO DO TEMPO DE VIDA DE PORTADORES EM DIODOS PIN OPERANDO COMO DISPOSITIVOS OPTOELETRÔNICOS

Vinícius Sousa de Morais<sup>1</sup>, Rodrigo Trevisoli Doria <sup>2</sup>

<sup>1,2</sup> Engenharia Elétrica, Centro Universitário FEI

unievinmorais@fei.edu.br e rtdoria@fei.edu.br

**Resumo:** Este artigo tem como principal objetivo o estudo do tempo de vida dos portadores no interior da região intrínseca de diodos PIN, visando determinar seu tempo médio a fim de permitir a otimização do comprimento desta região. Para tal, serão efetuadas simulações de diodos PIN, com uma porta sobre e região intrínseca, à qual deverá ser aplicado o método de bombeamento de cargas, visando determinar o tempo de vida dos portadores.

## 1. Introdução

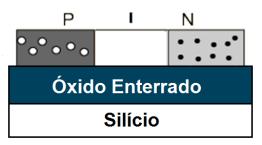

Um dos fotodetectores mais utilizados atualmente consiste no diodo PIN, o qual se assemelha a um diodo de junção PN, porém entre os materiais tipo P e tipo N existe uma região de baixa dopagem (~1x1015 cm-3), chamada de região intrínseca. Ao se polarizar este dispositivo reversamente, toda a região intrínseca ficará depletada e corresponderá a largura de depleção do fotodetector. Deste modo, a largura da região de depleção será definida pelo comprimento da região intrínseca [1]. A incidência de fótons de luz nesta região, fornece energia para os portadores, formando pares elétronlacuna. Estes pares dão origem a uma corrente elétrica dependente da intensidade e do comprimento de onda da luz incidente, o que torna possível seu uso como fotodetector. Na Figura 1, é apresentado o perfil bidimensional de um diodo fotodetector PIN.

Figura 1- Esquema bidimensional de um fotodiodo PIN Fonte:[1].

Uma forma de se otimizar a absorção de luzes de curtos comprimentos de onda em dispositivos de silício, consiste na utilização de diodos fotodetectores PIN fabricados em tecnologia SOI (Silicon-on-Insulator). Esta tecnologia tem se apresentado como uma alternativa para a tecnologia convencional na fabricação de circuitos integrados em altíssima escala de integração (Ultra Large Scale Integration – ULSI) [2]. Na tecnologia SOI, uma camada de material isolante separa a região ativa da lâmina do substrato, diminuindo a corrente de fuga proveniente do substrato [2]. Esta camada é chamada de óxido enterrado (Buried Oxide – BOX) uma vez que, normalmente, é composta de dióxido de silício (SiO<sub>2</sub>). Na Figura 2 é apresentado o esquema bidimensional de um fotodiodo PIN fabricado em tecnologia SOI.

Figura 2 - Representação esquemática bidimensional de um fotodiodo PIN fabricado em tecnologia SOI.. Fonte:[2]

Usualmente, a camada de silício acima do óxido enterrado apresenta espessura de algumas dezenas ou poucas centenas de nanômetros. Uma espessura desta camada é suficiente para absorver de forma efetiva luzes de pequenos comprimentos de onda (ultravioleta e azul). Para a absorção comprimentos de luz maiores, seria necessária uma camada de silício mais espessa.

Na aplicação de diodos PIN operando como fotodetectores, devemos saber o máximo comprimento de canal possível para uma maior geração de energia. Para comprimentos muito curtos a área de incidência de luz é pequena, o que limita a corrente gerada e, consequentemente, a capacidade de detecção de luz, enquanto que, para comprimentos muito longos, parte dos pares elétron-lacuna gerados acabam se recombinando, o que se traduz em uma redução da corrente. Com isso é fundamental saber o tempo de vida dos portadores livres. Através dele pode-se determinar o comprimento ótimo da região intrínseca para que seja gerada a máxima corrente.

A corrente gerada também tem uma grande dependência com a temperatura, assim como o tempo de vida dos portadores. Em altas temperaturas, a agitação térmica dos portadores é maior, o que induz uma maior taxa de colisão dos portadores com a rede cristalina, diminuindo o seu tempo de vida.

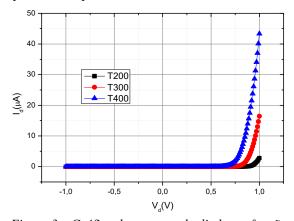

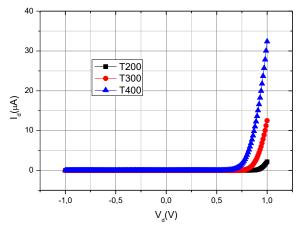

Dessa maneira, neste artigo, é apresentada uma análise da influência da temperatura e do comprimento da região intrínseca em um diodo PIN. A partir de simulações nas quais são variados ambos parâmetros, é possível obter a curva  $I_d \times V_D$  para entender seu real funcionamento.

### 2.Metodologia

Foram feitas simulações numéricas bidimensionais utilizando o simulador Sentaurus visando obter curvas características ( $I_dxV_d$ ) dos diodos PIN. Foram utilizados os seguintes parâmetros: tensão nos terminais variando de -1V à +1V, temperatura de 200, 300 e 400K, e

comprimentos de região intrínseca de  $8\mu m$  e  $10~\mu m$ . Cada uma das regiões tipo P e N apresentam comprimento de  $0.5\mu m$ . As camadas de silício e óxido enterrado apresentam espessuras de 80~nm e 390~nm, respectivamente.

### 3. Resultados Obtidos

Nas Figuras 3 e 4 são apresentadas as curvas de  $I_d$  x  $V_d$  para diodos com Li de 8 e 10  $\mu$ m operando em diferentes temperaturas, onde pode-se observar um aumento da corrente e uma redução da tensão de condução com o aumento da temperatura. Para se determinar a dependência entre  $I_d$  e  $V_d$ , identificamos uma relação entre a concentração intrínseca de portadores ( $n_i$ ) e a temperatura (T), vendo que quanto maior a temperatura maior será a concentração de portadores livres, conforme equação (1) [3].

$$n_i^2 = BT^3 e^{\left(-\frac{E_g}{kT}\right)} \tag{1}$$

onde B é um parâmetro dependente do material, Eg é a largura da faixa proibida do silício, k é a constante de Boltzmann.

Já a relação entre tensão de condução do diodo ( $V_{BI}$ ) e  $n_i$ , é inversamente proporcional, ou seja, quanto maior a concentração de portadores livres menor será a tensão de condução, como visto na equação (2)[4]

$$V_{Bl} = \frac{kT}{q} \ln \left( \frac{N_A N_D}{n_i^2} \right) \tag{2}$$

onde, T é a temperatura em kelvin, q é a carga elementar do elétron,  $N_{\scriptscriptstyle A}$  e  $N_{\scriptscriptstyle D}$  são as concentrações de dopantes do tipo P e N, respectivamente.

Figura 3 – Gráfico da corrente do diodo em função da tensão aplicada com comprimento do material intrínseco igual a 8μm (Li).

A partir das curvas  $I_d$  x  $V_d$  simuladas, pretende-se extrair o tempo de vida dos portadores livres, através da aplicação do método de bombeamento de cargas, em que uma tensão é aplicada à porta do diodo (Vf). Então, o tempo de vida é extraído através da equação (3)[5]:

$$\tau_{eff} = \frac{q.t_{si}.n_{i.w.l.}}{I_{m\acute{a}x}} \exp(\frac{qV_f}{2KT}) \tag{3}$$

. Onde q é carga do elétron,  $t_{si}$  a espessura do filme, w a largura, l o comprimento e Imáx a corrente máxima.

Figura 4 – Gráfico da corrente do diodo em função da tensão aplicada com comprimento do material intrínseco igual a 10µm (Li).

### 3. Conclusões

Nesta primeira etapa do projeto foi possível se aprofundar no estudo do diodo PIN diretamente polarizado, e identificar a relação inversamente proporcional entre a temperatura e a tensão de condução, devido à influência da concentração de portadores. Da mesma maneira, pode-se verificar a relação inversa entre a corrente e o comprimento do material intrínseco, devido ao aumento da resistência gerado a partir do aumento da distância que os portadores terão que fluir.

O passo subsequente será a simulação do diodo PIN com uma porta na região intrínseca, variando sua tensão de porta, e a partir dos resultados obtidos realizar a extração do tempo de vida dos portadores livres.

# 4. Referências

- [1] J. P. Colinge; C.A. Colinge, Physics of Semiconductor Devices, Springer, 436 p., 2006.

- [2] J.P. Colinge, Silicon-On-Insulator Technology: Materials to VLSI. 3rd Ed. Massachusetts: Kluwer Academic Publishers, 2004

- [3] SEDRA, S.; SMITH, K.. Microeletrônica. 4<sup>a</sup>. Edição, Pearson Makron Books, São Paulo, Brasil, 2005.

- [4] J.A. Martino, M.A. Pavanello, P.B. Verdonck, Caracterização elétrica de tecnologia e dispositivos MOS, Cengage Learning Editores, 2004.

- [5] T.Rudenko, V. Kilchytska, V. Dessard, D. Flandre. A revised reverse gated-diode technique for determining generation parameters in thinfilm silicon-on-insulator devices and its application at high temperatures, Journal of Applied Physics, 2005.

### Agradecimentos

À instituição Centro Universitário FEI pela disponibilização de equipamentos e utilização do software.

<sup>&</sup>lt;sup>1</sup> Aluno de IC do CNPq. Projeto com vigência de 08/19 a 07/20.