# ESTUDO DE TRANSISTORES SOI NMOS PARA IMPLEMENTAÇÃO DE MODELO EM VERILOG-A

Eric Grilo Araujo<sup>1</sup>, Michelly de Souza

Departamento de Engenharia Elétrica – Centro Universitário FEI

ericgrilo.a@gmail.com michelly@fei.edu.br

**Resumo:** Este projeto de iniciação científica tem como objetivo a implementação de um modelo analítico continuo para transistores SOI nMOS em linguagem Verilog-A, a fim de permitir a simulação analítica de circuitos analógicos em simuladores do tipo SPICE.

## 1. Introdução

Durante a fabricação de circuitos integrados o uso de transistores CMOS de dimensões extremamente reduzidas apresenta problemas provocados por diversos efeitos de canal curto. A tecnologia apresentada por transistores de tipo SOI tem sido de extrema importância para sustentar a redução de dimensões enfrentada pelo CMOS convencional. Com a tecnologia SOI (Silicon On Insulator) parte desses efeitos parasitários próprios da tecnologia CMOS convencional, como as capacitâncias de junção entre fonte/dreno e substrato, sofrem uma redução devido à camada de isolante existente na tecnologia SOI (Óxido enterrado) entre o dispositivo e a lâmina de silício [1]. Além disso, a fabricação desses dispositivos é bem mais simples quando comparada com a fabricação de transistores com tecnologia MOS convencional, devido à ausência de cavidades.

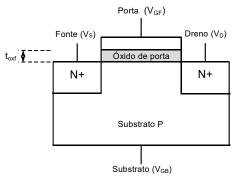

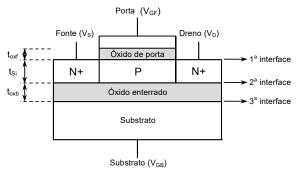

As figuras 1 e 2 apresentam respectivamente o perfil transversal de um transistor nMOS feito com a tecnologia CMOS convencional e de um transistor nMOS feito com a tecnologia SOI, indicando os eletrodos de porta ( $V_{GF}$ ), substrato ( $V_{GB}$ ), fonte ( $V_{S}$ ) e dreno ( $V_{D}$ ), as espessuras dos óxidos de porta ( $t_{oxf}$ ) e enterrado ( $t_{oxb}$ ) e da camada de silício ( $t_{Si}$ ), bem como as três interfaces Si–SiO<sub>2</sub> existentes na estrutura SOI.

Figura 1 – Perfil transistor nMOSFET tecnologia MOS convencional.

Figura 2 – Perfil transistor nMOSFET tecnologia SOI.

Transistores SOI apresentam diversas vantagens do ponto de vista analógico, tais como maior relação entre a transcondutância e a corrente de dreno e menor inclinação de sublimiar [2]. Para que seja possível o projeto de circuitos analógicos é necessário utilizar simulações de tipo SPICE. Para que ocorra a simulação é necessário a existência de um modelo analítico contínuo do componente, que seja capaz de descrever sua corrente de dreno em todas as condições de polarização.

Neste trabalho, será realizada a implementação de um modelo analítico contínuo para transistores SOI em linguagem Verilog-A [3], que é válida para qualquer simulador do tipo SPICE.

## 2. Transistores SOI MOSFET

A espessura da camada de silício, a concentração de dopantes e a temperatura são fatores que diferenciam os transistores SOI MOSFET. Baseado nessas três características podemos classificar esses transistores de três formas, sendo FDSOI (totalmente depletado ou de camada fina), PDSOI (parcialmente depletado ou de camada espessa) ou NFDSOI (quase totalmente depletado ou de camada media) [2].

O dispositivo classificado com FDSOI apresenta a espessura da camada de silício menor que a espessura máxima da região de depleção, fazendo com que exista uma interação entre as regiões de depleção induzidas pela porta e pelo substrato [2].

Esses dispositivos são os que apresentam maior vantagem em relação ao MOS convencional. Dentre essas vantagens destacam-se a diminuição de efeitos de canal curto, maior mobilidade de portadores, menor variação de tensão limiar em relação a temperatura, aumento da transcondutância e diminuição das capacitâncias parasitárias de fonte/dreno [1, 2].

## 3. Modelo Analítico Contínuo para Transistores SOI nMOSFET

O modelo analítico utilizado nesse projeto, proposto por Iñiguéz et al [4], baseia-se na física de funcionamento de transistores FD SOI e é continuo em todos os regimes de inversão, o que é necessário para simuladores de tipo SPICE. Além disso, apresenta poucos parâmetros de ajuste quando comparado com outros modelos. Neste modelo, a corrente de dreno é dada por:

$$I_{DS} = \mu_n \frac{W}{L} \left[ v_T \left( Q_{nf,D} - Q_{nf,S} \right) - \frac{Q_{nf,D}^2 - Q_{nf,S}^2}{2nC_{oxf}} \right]$$

(1)

onde  $Q_{nf,D}$  e  $Q_{nf,S}$  são as densidades de carga de inversão nas fronteiras do canal com as regiões de dreno e fonte, dadas em função das tensões aplicadas:

$$Q_{nf} = -C_{oxf}nv_{T}S_{NT} \cdot ln \left[ 1 + \frac{-Q_{0}}{nv_{T}S_{NT}} exp\left(\frac{V_{GF} - nV_{thfi} - nV_{C}}{nv_{T}}\right) + exp\left(\frac{V_{GF} - V_{thf} - nV_{C}}{nv_{T}S_{NT}}\right) \right]$$

$$(2)$$

onde  $V_{thf}$  e  $V_{thfi}$  são as tensões de limiar obtidas em inversão forte e fraca,  $Q_0$  é a carga de inversão para  $V_{GF} = V_{thfi}$  [2].

A Tabela 1 apresenta a lista de parâmetros deste modelo:

Tabela 1 – Parâmetros do modelo analítico.

| Parâmetro        | Descrição                                          |

|------------------|----------------------------------------------------|

| L                | Comprimento de canal                               |

| W                | Largura de canal                                   |

| $t_{Si}$         | Espessura da camada de silício                     |

| t <sub>oxf</sub> | Espessura do óxido de porta                        |

| t <sub>oxb</sub> | Espessura do óxido enterrado                       |

| N <sub>A</sub>   | Concentração de dopantes no canal                  |

| $\mu_{\rm n}$    | Mobilidade efetiva de portadores no                |

|                  | canal                                              |

| α                | Fator de degradação da mobilidade                  |

| V <sub>sat</sub> | Velocidade de saturação dos portadores             |

| S <sub>NT</sub>  | Parâmetro de ajuste que controla a                 |

|                  | transição entre inversão fraca e forte             |

| A <sub>TS</sub>  | Parâmetro de ajuste que controla a                 |

|                  | transição entre triodo e saturação                 |

| l <sub>c</sub>   | Comprimento característico                         |

| σ                | Parâmetro que considera o efeito do                |

|                  | aumento de V <sub>D</sub> sobre a tensão de limiar |

## 4. Linguagem Verilog-A

Verilog-A é uma linguagem de descrição de hardware usada para modelar sistemas eletrônicos ao nível de circuito e se refere exclusivamente a parte analógica de Verilog-AMS, linguagem esta desenvolvida para descrição de comportamentos de circuitos elétricos analógicos e de sinais misto [3, 5]. Essa linguagem apresenta facilidade de portabilidade entre diversos simuladores.

A linguagem Verilog-A se refere à parte de descrição analógica da linguagem Verilog-AMS (analog and mixed

signal), que surgiu para substituir a linguagem C e FORTRAN na descrição de componentes e circuitos [3]. SPICE sempre foi muito efetivo na simulação de circuitos analógicos e digitais e atualmente é o mais utilizado. Antigamente era limitado ao uso de componentes primitivos e esse problema era resolvido utilizando programas como Matlab, porém tais programas não se comunicavam com o simulador. Com o Verilog-A é possível fazer uma descrição matemática de componentes diretamente no simulador, facilitando a simulação de circuitos analógicos [6]. Os simuladores utilizam a lei de Kirchoff para formular as equações do circuito. Em Verilog-A os componentes devem ser descritos entre dois nós.

#### 5. Conclusões

De acordo com a revisão bibliográfica realizada até o momento é possível notar que transistores com a tecnologia SOI apresentam uma significante redução de efeitos parasitários quando comparado com os transistores MOS convencionais. Também se percebe que a escolha da linguagem utilizada na implementação do modelo é adequada devido ao fato de diversos simuladores tipo SPICE aceitarem modelos escritos em Verilog-A.

Na continuação desse trabalho será realizada a implementação do modelo em Verilog-A e a sua validação comparando resultados obtidos de simulações com dados experimentais já medidos para transistores FDSOI.

## 6. Referências

- [1] B. El-Kareh. et al; Silicon on insulator-an emerging high-leverage technology. IEEE Transactions on Components, Packaging, and Manufacturing Technology, v. 18, n. 1, p. 187-194, 1995.

- [2] J. P. Colinge. Silicon-On-Insulator Technology: Materials to VLSI, 3 Ed. Massachusetts (EUA): Kluwer Academic Publishers, 2004.

- [3] MOREIRA, C. V. Implementação do modelo contínuo estático e dinâmino de nanofios transistores mos sem junções usando linguagem verilog-a para projeto de circuitos cmos. 2018. Dissertação de Mestrado. Centro Universitário FEI, São Bernardo do Campo. p. 132, 2018.

- [4] IÑIGUEZ, B.; FERREIRA, L.F.; GENTINNE, B.; FLANDRE, D. A Physically-Based C<sub>∞</sub>-Continuous Fully-Depleted SOI MOSFET Model for Analog Applications, <u>IEEE Trans. Electron Devices</u>, v.43, n.4, p.568-575, 1996.

- [5] MCANDREW, Colin C. et al. Best practices for compact modeling in Verilog-A. IEEE J. Electron Devices Soc, v. 3, n. 5, p. 383-396, 2015.

- [6] FITZPATRICK, Dan; MILLER, Ira. Analog behavioral modeling with the Verilog-A language. Springer Science & Business Media, 1998.

<sup>&</sup>lt;sup>1</sup> Aluno de IC do Centro Universitário FEI. Projeto com vigência de 04/17 a 03/18.