# COMPARAÇAO DO DESEMPENHO DE TRANSISTORES CONVENCIONAIS E SOI MOSFETS APLICADOS A ESPELHOS DE CORRENTE

Bianca Tavares Serra Gil<sup>1</sup>, Rodrigo Trevisoli Doria<sup>2</sup>

<sup>1</sup> Etec Lauro Gomes

<sup>2</sup> Departamento de Engenharia Elétrica - Centro Universitário FEI biancatsgil@gmail.com; rtdoria@fei.edu.br

**Resumo:** Neste trabalho, foram feitas diversas simulações com transistores SOI MOSFETs e convencionais em circuitos unitários e com espelhos de corrente, visando observar como os transistores fabricados na tecnologia SOI se comportam em relação aos transistores convencionais. Pôde-se observar que, ao serem aplicados a espelhos de corrente, transistores SOI apresentam uma melhor precisão de espelhamento em relação a convencionais de dimensões similares.

## 1. Introdução

Transistores fabricados na tecnologia metal-óxidosemicondutor (MOS), desde meados da década de 60, são os componentes eletrônicos mais utilizados em circuitos integrados. Na maioria dos casos dos chips fabricados atualmente, este componente é utilizado como base. A indústria da microeletrônica tem investido grandemente redução dimensões na nas dispositivos, buscando uma maior utilização de transistores por *chip*, sem consequentemente aumentar a sua área e sua potência dissipada, pois quanto maior o número de transistores MOS utilizados em um chip, sua capacidade de processamento aumenta.

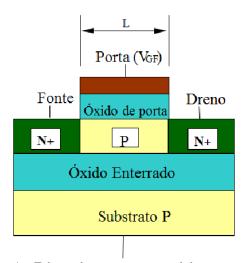

O transistor MOS apresenta quatro terminais, como pode ser observado na figura 1, denominados como dreno (V<sub>D</sub>), fonte (V<sub>S</sub>), porta (V<sub>G</sub>) e substrato (V<sub>B</sub>). De modo simplificado, pode-se dizer que o transistor MOS pode ter duas funções principais. Em circuitos digitais sua principal função consiste em permitir ou não a condução de corrente entre dois pontos, aos quais são conectados os terminais de dreno e fonte. Já, em circuitos analógicos, o transistor é responsável por controlar a corrente que fluirá entre os terminais de fonte e dreno [1,2,3].

Porém, ao fazer uma redução de suas dimensões para valores extremos, há algumas ocorrências no interior dos dispositivos alguns efeitos de segunda ordem, denominados efeitos de canal curto, que degradam suas características elétricas. Assim, novas tecnologias foram desenvolvidas, visando miniaturização dos transistores MOS com uma menor ocorrência de efeitos de canal curto [2]. Dentre estas tecnologias, pode ser citada a tecnologia Silício-Sobre-Isolante – SOI (Silicon-On-Insulator). Nesta tecnologia, uma camada de isolante, denominada óxido enterrado (BOX - Buried Oxide), separa a região ativa da lâmina, onde será fabricado os transistores MOS, do substrato de silício [4]. Esta configuração melhora a relação entre capacitâncias, ou acoplamento capacitivo da estrutura. Por esta razão, as características elétricas de transistores fabricados em tecnologia SOI são sensivelmente

melhores às apresentadas por transistores fabricados em tecnologia MOS convencional. Na Figura 1, é apresentado o esboço da seção transversal de um transistor MOS fabricado em tecnologia SOI.

Figura 1 – Esboço da seção transversal de um transistor MOS fabricado em tecnologia SOI.

Visando comparar o desempenho de transistores SOI em relação a MOS convencionais operando em pequenos circuitos elétricos, foi proposto o estudo destes dispositivos operando como espelhos de corrente. Tais circuitos são extremamente comuns em sistemas microeletrônicos, visto que podem ser utilizados para replicar a corrente gerada em uma fonte de corrente para diversos ramos de um mesmo circuito. Desta maneira, pode-se verificar o desempenho de transistores SOI em relação a MOS convencionais a partir da precisão de espelhamento da corrente de entrada para os demais ramos do circuito [1].

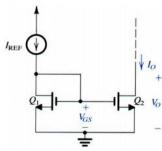

Embora existam diversas configurações do circuito do espelho de corrente, neste trabalho foi utilizada a configuração mais simples, cujo esquema elétrico está disposto na Figura 2. O principal objetivo dos espelhos de corrente é que a corrente do ramo de saída ( $I_0$ ) seja igual à aplicada no ramo de entrada ( $I_{REF}$ ). Deste modo, a melhor forma de se avaliar o desempenho destes circuitos consiste na observação da razão entre  $I_0$  e  $I_{REF}$  para diferentes condições de polarização do ramo de entrada.

Logo, o projeto atual teve como objetivo a simulação Spice de espelhos de corrente compostos por transistores SOI, cujos resultados foram comprados com os de simulações efetuadas com transistores MOS convencionais.

Figura 1 – Circuito elétrico de um espelho de corrente em arquitetura convencional.

### 2. Metodologia

O trabalho atual foi desenvolvido em cinco etapas principais, que consistiram nos estudos bibliográficos básico e específico de transistores MOS, tecnologia SOI e espelhos de corrente, na simulação Spice de transistores convencionais e SOI unitários e em circuitos espelhos de corrente com diferentes polarizações e na análise dos dados obtidos. Foram feitas simulações computacionais Spice no *software* ICAP 4 [5] e as curvas foram construídas no software Origin8, em que foram feitas geradas curvas a partir de Iref e V<sub>0</sub>.

#### 3. Resultados

Como mencionado anteriormente, foram executadas simulações Spice utilizando-se o software Icap 4 para circuitos espelhos de corrente considerando transistores MOS convencionais e SOI com características similares tais como comprimento de canal de 1 µm, espessura de óxido de porta de 30 nm e concentração de dopantes de fonte e dreno de 1x10<sup>20</sup> cm<sup>-3</sup>. Os transistores SOI apresentam espessura da camada de óxido enterrado de 400 nm e concentração de dopantes de 1x10<sup>15</sup> cm<sup>-3</sup> na região de canal, enquanto que os transistores convencionais apresentam concentração de dopantes na região de canal de 1x10<sup>17</sup> cm<sup>-3</sup>.

As simulações foram efetuadas circuitos idênticos ao da Figura 2, em que foi considerada uma fonte de corrente  $I_{REF}$  fixa na entrada em que foram aplicadas diferentes polarizações desde 5 mA até 50 mA com passos de 5 mA. Para cada um dos casos a tensão de saída  $V_0$  foi variada de 0 a 3V.

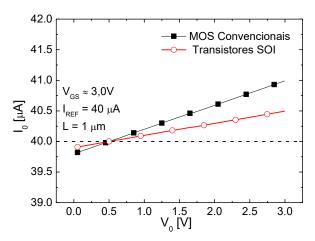

Na Figura 3 é apresentado um gráfico da corrente de saída I<sub>0</sub> em função da tensão de saída V<sub>0</sub> para um espelho de corrente comporto por transistores convencionais e outro por transistores SOI, ambos para uma polarização de entrada I<sub>REF</sub> = 40 mA. Como podese observar, a corrente se mantém praticamente constante com o aumento da tensão para ambos os casos, por conta do espelho de corrente. Entretanto, pode-se notar que curva da corrente em função da tensão para o transistor SOI apresenta menor variação e menor erro em relação aos 40 mA aplicados na entrada, que a obtida em transistores convencionais, o que pode ser explicado pelo melhor acoplamento capacitivo, apresentado por transistores SOI em relação a transistores MOS convencionais, o que está relacionado à camada de óxido enterrado.

Figura 2 – Gráfico da tendência de tensão de limiar obtida pelo método da segunda derivada em função de TSi pra diferentes comprimentos de canal L.

#### 4. Conclusões

Podemos concluir com esta IC que os transistores SOI MOSFETs são de extrema importância no mercado atual, como na evolução da microeletrônica. Como visto, quanto mais transistores MOSFETs em um chip maior é seu processamento, porém dependendo da diminuição das dimensões para valores extremos, podem ocorrer os efeitos de canal curto. Daí o desenvolvimento de novas tecnologias como a SOI. Em relação aos transistores SOI MOSFETs aplicados a espelhos de corrente é nítido que tais dispositivos espelham a corrente da forma bem mais constante que transistores MOS convencionais, ao se variar a tensão do ramo de saída, o que está relacionado ao melhor acoplamento capacitivo da estrutura.

#### 5. Referências

- [1] Microeletrônica, Sedra & Smith, 5<sup>a</sup> ed., Cap 4, p. 141-155 (até item 4.2.3) e 164-167 (item 4.4 até 4.4.4); Cap 6, p. 353, 354 (item 6.3.1), 407, 408 (item 6.12.1) e 410 (item 6.12.4).

- [2] MARQUES, Eduardo Ângelo B.; JÚNIOR, Salomão Choueri; CRUZ, Eduardo Cesar Alves. Dispositivos Semicondutores: Diodos e Transistores. 13 ed. Rev. São Paulo: Érica 2012. p.333-348.

- [3] SITE:http://www.newtoncbraga.com.br/index.php/como-funciona/6417-art977

- [4] J.P .Colinge, Silicon-on-Insulator Technology: Materials to VLSI, 3ª Edição ed., Boston: Kluwer Academic Publishers, 2003, p. 366.

- [5] ICAP 4 Spice Simulator, Manual do Usuário, Intusoft, 2016.

#### Agradecimentos

Ao Centro Universitário FEI pela realização das medidas ou empréstimo de equipamentos e ao meu orientador Rodrigo Trevisoli Dória que foi crucial para a realização nesse trabalho

<sup>1</sup>Aluno de IC-EM do CNPq – Etec Lauro Gomes. Projeto com vigência de 04/17 a 09/18.