# EFEITO DA VARIABILIDADE DA CONCENTRAÇÃO DE DOPANTES NAS CARACTERÍSTICAS ELÉTRICAS DE TRANSISTORES SOI SEM JUNÇÕES

Danilo Henrique Bento dos Santos<sup>1</sup>, Rodrigo Trevisolli Doria<sup>2</sup>

<sup>1,2</sup>Engenharia Elétrica, Centro Universitário da FEI

<sup>1</sup>uniedansantos@fei.edu.br

<sup>2</sup>rtdoria@fei.edu.br

**Resumo:** Transistores de efeito de campo do tipo Metal-Óxido-Semicondutor ou MOSFET constituem o principal dispositivo eletrônico utilizado na indústria de circuitos integrados. Assim, o projeto atual visa à simulação das características elétricas de transistores sem junções na tecnologia silício-sobre-isolante (SOI) através de ferramentas de projeto auxiliado por computador, considerando a influência da concentração de dopantes e contribuindo para um modelo físico de variabilidade em transistores sem junções.

## 1. Introdução

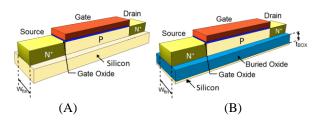

A capacidade de processamento dos computadores depende diretamente da quantidade de transistores, de maneira que os circuitos integrados responsáveis pelo processamento das informações em computadores de tecnologia atual, podem ser compostos por alguns bilhões de transistores MOSFET. A evolução na quantidade de transistores por chip observada ao longo das últimas décadas só tem sido possível graças à redução das dimensões dos dispositivos. Visando a fabricação de transistores cada vez menores sem que suas características elétricas fossem severamente degradadas, foram desenvolvidas diversas tecnologias alternativas, como o caso da tecnologia silício-sobreisolante, ou SOI (Silicon-on-Insulator), em que uma camada de óxido dielétrico é introduzida entre a região ativa da lâmina e o substrato, e da tecnologia de múltiplas portas em que mais de uma face da camada de silício é coberta pelo material de porta, proporcionando melhor acoplamento capacitivo à estrutura. Na Figura 1, são apresentados cortes tridimensionais de longitudinais de transistores fabricados na tecnologia convencional (A) e na tecnologia SOI (B).

Figura 1 – Esboço tridimensional (A) de um transistor nMOS convencional e (B) de um transistor nMOS-SOI.

Diversos transistores de múltiplas portas, comumente denominados de transistores 3D como os FinFETs de porta dupla ou tripla e os dispositivos de canal circundante, têm recebido bastante atenção da comunidade científica graças ao seu bom desempenho em aplicações digitais. Entretanto, um outro transistor de múltiplas portas, denominado transistor MOS sem junções ou JNT (*Junctionless Nanowire Transistor*), tem demonstrado resultados bastante promissores, além de permitir um escalamento ainda maior dos dispositivos. Neste transistor, as regiões de fonte, dreno e canal apresentam um mesmo tipo e concentração de dopante eliminando as junções PN, permitindo sua fabricação a partir de um processo relativamente simples. Entretanto, para funcionar como projetado, transistores sem junções precisam ter concentração de dopantes da ordem de  $10^{18}$ - $10^{19}$  cm<sup>-3</sup> na região de canal.

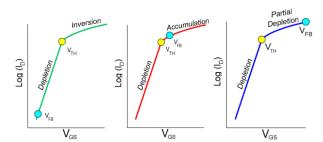

Com o intuito de simplificar o processo de fabricação de transistores MOS com tecnologia sub-16 nm, foi criado um dispositivo MOS de porta tripla, chamado de transistor MOS sem junções ou JNT. A Figura 2 descreve as curvas do logaritmo da corrente de dreno ( $I_D$ ) versus a tensão entre porta e fonte para os dispositivos modo inversão (A), modo acumulação (B) e JNT (C). Nota-se que no JNT a diferença entre a tensão de faixa plana (ou *flatband voltage* –  $V_{FB}$ ) e a tensão de limiar (*threshold voltage* –  $V_{TH}$ ) é maior que no dispositivo modo acumulação.

Figura 2 – Curvas do logaritmo da  $I_D$  versus  $V_{GS}$  para os dispositivos modo inversão (A), modo acumulação (B) e sem junções (C) [1].

Deste modo, para transistores de dimensões extremamente pequenas, apenas algumas dezenas de átomos de dopantes estarão presentes da região de canal. Assim, uma pequena variabilidade na concentração de dopantes pode afetar de forma significantes as características elétricas destes transistores. Para entender melhor como o efeito da variabilidade na concentração de dopantes afeta as características elétricas dos JNTs, são necessárias simulações de suas curvas de corrente vs. tensão, bem como medidas experimentais. Tais resultados obtidos neste projeto irão compor um modelo físico que considere a variabilidade nestes dispositivos.

### 3. Metodologia

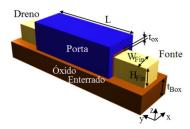

Nas etapas iniciais do projeto foram implementados no simulador Sentaurus dois códigos de simulação. No primeiro foram definidas as variáveis que representam as dimensões do JNT, conforme Figura 3, sendo elas: L<sub>fin</sub>, comprimento de canal; H<sub>fin</sub>, altura do fin; L ou L<sub>fd</sub>, comprimento das regiões de fonte e dreno; tox, espessura da camada do óxido de porta; tbox, espessura do óxido enterrado; N<sub>D</sub>, concentração de dopantes no silício; e W<sub>fin</sub>, largura do fin. No segundo código, foram gerados os dados de saída com as características I-V para cada dispositivo nas configurações observadas, bem como algumas variáveis adicionais, definidas temperatura (T) em Kelvin, tensão de substrato (V<sub>BS</sub>) e tensão no dreno (V<sub>DS</sub>). Os valores definidos seguem na Tabela I e II.

Figura 3 – Representação de Estrutura dos Dispositivos de Porta Tripla [2].

Tabela I – Valores definidos para as variáveis no Sentaurus Structure Editor (SDE).

| L <sub>fin</sub><br>[nm] | H <sub>fin</sub><br>[nm] | W <sub>fin</sub><br>[nm] | L <sub>fd</sub><br>[nm] | t <sub>ox</sub><br>[nm] | t <sub>box</sub><br>[nm] | $N_{\rm D}$ [ $10^{18}~{ m cm}^{-3}$ ] |

|--------------------------|--------------------------|--------------------------|-------------------------|-------------------------|--------------------------|----------------------------------------|

| 100                      | 10                       | [9-12]                   | 30                      | 1,5                     | 150                      | [9-11]                                 |

Tabela II – Valores definidos para as variáveis adicionais no Sentaurus Device.

| T<br>[K] | V <sub>BS</sub> [V] | V <sub>DS</sub><br>[V] |  |

|----------|---------------------|------------------------|--|

| 300      | 0                   | [0,05, 1]              |  |

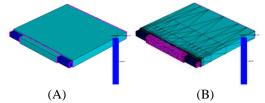

Como a variação da largura do fin ( $W_{fin}$ ) é um dos objetos de estudo desse projeto, adotou-se quatro valores diferentes. Dessa forma, foram geradas quatro estruturas, uma para cada valor de Wfin. Isso foi adotado também para concentração de dopantes ( $N_D$ ), sendo observado três valores para cada estrutura. Na Figura 4 temos a representação de um dos dispositivos.

Uma vez determinados os dados de saída com as características I-V para cada dispositivo através das simulações executadas, a fim de investigar o efeito da variabilidade da concentração de dopantes nas características elétricas dos JNT, foi adotado o método da segunda derivada (DD) da curva  $I_D \, x \, V_{GS} \, [1]$ , isto é, a transcondutância, para obtenção da Tensão de Limiar ( $V_{TH}$ ) dos dispositivos.

$\label{eq:Figura 4-Representação no Sentaurus Visual} \ da estrutura (A) e da malha associada (B) nas interfaces \ do dispositivo (<math>N_D = 10^{19} \ cm^{-3}$ ).

### 4. Resultados

Inicialmente, na Figura 5 são apresentadas as curvas de log  $(I_D)$  x  $V_{GS}$  e extração da tensão de limiar (*Threshold Voltage* –  $V_{TH}$ ) pelo método da segunda derivada (DD) para os JNT de diferentes larguras ( $W_{fin}$ ), considerando  $V_{DS}=0{,}05$  V e  $N_D=10^{19}\,\mathrm{cm}^{-3}$ .

Figura 5 – Curva log ( $I_D$ ) x  $V_{GS}$  de dispositivos com diferentes larguras ( $W_{fin}$ ) e extração da  $V_{TH}$  (B).

Finalmente, analisamos a influência da variação na concentração de dopantes ( $N_D$ ) na tensão de limiar (VTH) dos dispositivos, conforme representação para o dispositivo  $W_{\text{fin}} = 12$  nm na Figura 6 a seguir.

$\label{eq:Figura} \begin{array}{l} Figura~6-Curva~log~(I_D)~x~V_{GS}~de~dispositivos~com\\ diferentes~N_D~e~extração~da~V_{TH}~(B). \end{array}$

# 5. Conclusões

Nesta etapa do projeto, foi verificado tanto a influência de fatores dimensionais, como  $W_{fin}$ , largura do fin, bem como a variabilidade da concentração de dopantes na tensão de limiar dos JNTs estudados. Como próximos passos, temos a validação dos dados de simulação via medidas experimentais nos dispositivos.

### 6. Referências

[1] J.P. Colinge, A. Kranti, R. Yan, C.-W. Lee, I et. al., "Junctionless Nanowire Transistor (JNT): Properties and design guidelines," Solid-State Electronics, pp. 33-37, 2011.

[2] R. Trevisoli., "Operação e Modelagem de Transistores MOS Sem Junções", Tese de Doutorado – USP, Brasil, 2013.

<sup>1</sup> Aluno no Programa PIBIC do Centro Universitário da FEI. Projeto com vigência de 10/2021 a 09/2022.