# Efeitos de Radiação Ionizante em MOSFETS de diferentes geometrias

Paulo Roberto Garcia Junior<sup>1</sup>, Marcilei Guazzelli<sup>2</sup>

<sup>1</sup> Departamento de Engenharia Elétrica, FEI

<sup>2</sup> Departamento de Física, FEI

<u>uniepajunior@fei.edu.br</u>, <u>marcilei@fei.edu.br</u>

**Resumo:** Este estudo visa analisar os efeitos da Dose Total Ionizante (TID) em layouts de MOSFET ELT e em layouts convencionais de porta retangular, comparando suas tolerâncias à TID. Os dispositivos sob teste foram expostos a uma dose total acumulada de 300 krad(Si) de raios X de 10 keV. Os resultados sugerem que, para os parâmetros de tensão de limiar e corrente de fuga, o layout ELT não demonstra uma maior tolerância à TID em comparação com o dispositivo de porta retangular.

## 1. Introdução

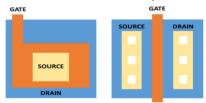

O Enclosed Layout Transistor (ELT) é um layout distinto de transistor MOS caracterizado por uma forma única, onde as regiões de dreno ou fonte são completamente envolvidas em polisilício. Essa característica estrutural elimina o transistor lateral parasita, que em transistores retangulares aparece na interface com o óxido de isolamento lateral, efetivamente reduzindo parte da corrente de fuga [1].

A Figura 1 apresenta uma ilustração de uma estrutura ELT com isolamento adicional em torno do terminal de fonte (lado esquerdo), comparada com uma estrutura convencional de MOSFET (lado direito).

Figura 1 - ELT (lado esquerdo) e retangular (lado direito)

Os efeitos da TID são causados pelo acúmulo de carga principalmente nas regiões de óxido e interfaces de óxido e silício [1,2-3], devido à radiação ionizante que atinge os dispositivos. Uma vez que a estrutura ELT apresenta uma área de polissilício no dispositivo, reduzindo a área de óxido [4], ela é considerada uma candidata a sofrer menos danos pela TID. Desta forma, este trabalho apresenta o comportamento do MOSFET ELT durante a aplicação de doses de radiação ionizante, acumuladas até 300 krad(Si) com uma taxa de dose igual a 100 krad(Si)/h.

## 2. Material e metodologia

O grupo de designers do CTI (Centro de Tecnologia da Informação) forneceu dois circuitos integrados, cada um com cinco dispositivos P-MOSFET de tecnologia SOI-CMOS de 0,6  $\mu m$ , sendo três deles com layout retangular e os outros dois dispositivos com estruturas de layout ELT.

Para analisar o comportamento dos dispositivos aos efeitos da TID, os dispositivos foram caracterizados antes, durante e após a exposição ao feixe de raios-X. Foram adquiridas as curvas I-V em dois modos de polarização diferentes, denominados ON MODE e OFF MODE.

Durante a irradiação em ON MODE, os dispositivos foram polarizados com  $V_{GS} = -5$  V e  $V_{DS} = 0$  V, enquanto na irradiação OFF MODE, todos os terminais foram aterrados. O procedimento de irradiação utilizou um difratômetro Shimadzu XRD-6100, operando com uma corrente controlada de 30~mA, resultando em uma taxa de dose de 100~krad(Si)/h. A caracterização foi realizada de modo que cada circuito foi irradiado em um dos modos de polarização diferentes e acumulou uma dose de 300~krad(Si), seguida por uma semana de *Annealing* em Temperatura Ambiente (RTA: *Room Temperature Annealing*).

A caracterização elétrica I-V foi realizada usando o sistema portátil NI-PXIe-1062Q, as medições foram feitas antes, durante e após a exposição à irradiação. Durante a caracterização, a tensão entre os terminais Fonte-Dreno ( $V_{DS}$ ) foi de -10,0 mV e foi aplicada em ambos os modos de irradiação, variando a tensão Gate-Fonte ( $V_{GS}$ ) de 1,0 V a -5,0 V. As medidas foram feitas em intervalos de 20 minutos e medidas adicionais foram realizadas uma semana depois para analisar a recuperação em R.T.A.

Os dados extraídos foram submetidos a análise estatística e os resultados do estudo apresentarão uma comparação entre a média dos valores extraídos em cada layout em cada modo de irradiação.

## 3. Resultados

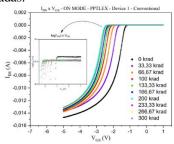

A Figura 2 apresenta algumas das curvas  $I_{DS}$  x  $V_{GS}$  do dispositivo retangular analisadas neste estudo durante o ON MODE. É possível perceber um deslocamento para a esquerda em todos os dispositivos e modos de polarização, o que indica a captura de cargas na área de óxido [3]. O comportamento apresentado na figura 2, foi verificado em todas as curvas analisadas.

Figura 2 – Comportamento das curvas características

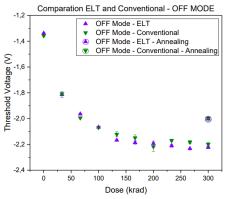

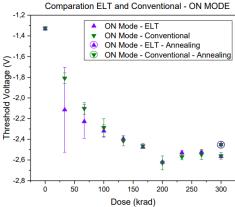

O primeiro parâmetro analisado foi a tensão de limiar ( $V_{TH}$ ), extraída pelo método da segunda derivada da curva característica I-V [5]. Com esses dados, foi possível traçar dois gráficos. A Figura 3 mostra uma comparação entre o MOSFET convencional (retangular) e o ELT no OFF MODE e a Figura 4 apresenta uma comparação entre os dois layouts no ON MODE.

Figura 3 - Comparação do  $V_{TH}$  no OFF MODE

Figura 4 - Comparação do V<sub>TH</sub> no ON MODE

Utilizando a curva  $log(I_{DS})$  x  $V_{GS}$  com um ajuste linear na área inicial da curva ( $V_{GS}=0.5V$ ), é possível extrair a corrente de fuga do transistor ( $I_{DS-LEAK}$ ) [5]. Com esses dados, foi possível traçar dois novos gráficos.

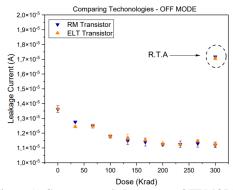

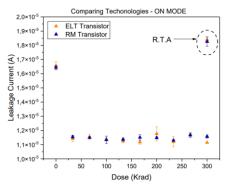

A Figura 5, é apresentada uma comparação entre o layout convencional e o ELT no OFF MODE, enquanto a Figura 6 mostra uma comparação entre os dois layouts no ON MODE.

Figura 5 - Comparação do Ids-Leak no OFF MODE

Figura 6 - Comparação do I<sub>DS-LEAK</sub> no ON MODE

#### 4. Conclusões

Uma das consequências da radiação ionizante em transistor é o aprisionamento de cargas na região de óxido do terminal de porta, o que causará o deslocamento da tensão de limiar [1]. Esse comportamento foi observado nos resultados das curvas de tensão de limiar, que indicam que ambas as tecnologias são sensíveis aos efeitos da TID para esse parâmetro.

Foi observado um aumento na corrente de fuga em ambas as tecnologias, enquanto era esperado uma maior estabilidade nos transistores com layout ELT [4]. Isso ocorreu porque a retenção das cargas tornou-se mais significativa do que a geométrica do aparelho, a qual apresenta uma grande região de óxido. As correntes de fuga se apresentaram maior do que o valor inicial após as cargas se estabilizarem no dispositivo com o *Annealing* [3]. Apesar dos resultados negativos para a corrente de fuga neste estudo utilizando TID por raios X, o layout ELT ainda é uma boa estratégia para evitar a corrente de fuga em transistores [3].

Em relação aos parâmetros de tensão de limiar e corrente de fuga, os resultados deste estudo indicam que os efeitos da TID induziram uma degradação semelhante nos dispositivos em teste devido à exposição a raios X de 10 keV a uma taxa de dose de 100 krad(Si)/h.

#### 5. Referências

- OLDHAM, T.R. "Total Ionizing Dose Effects in MOS oxides and Devices". IEEE Transactions on Nuclear Science v.50, p.483, 2003..

- [2] L E Seixas Jr et al., "Study of proton radiation effects among diamond and rectangular gate MOSFET layouts", 2017 Mater. Res. Express 4 015901DOI 10.1088/2053-1591/4/1/015901

- [3] SILVEIRA, M. A. G, et al. "Electric field and temperature effects in irradiated MOSFETs." AIP Conference Proceedings v.1753, p.080004, 2016.

- [4] COLINGE, J. P.; COLINGE, C. A. Physics of Semiconductor Devices. [S.l.]: Springer US, 2007.

- [5] J.A. Martino, M.A. Pavanello, P.B. Verdonck. Caracterização Elétrica de Tecnologia e Dispositivos MOS. São Paulo: Thomson, 2003.

#### Agradecimentos

Os autores agradecem o apoio financeiro das agências de financiamento. FAPESP, Brasil 2022/09131-0, 2018/25225-9, 2020/04867-2, 2019/07767-1, 2018/25225-9; CITAR: Proc. 01.12.0224.00; INCTFNA, Proc. 464898/2014-5; CNPq: 408800/2021-6, 301576/2022-0, 306360/2020-9.