About

Current Positions

Full professor at the Electrical Engineering Department at Centro Universitário FEI, São Bernardo do Campo, Brazil.

Coordinator of Scientific Initiation Program at Centro Universitário FEI.

Head of Semiconductor Devices Research Group at FEI.

Administrative Director at Brazilian Microelectronics Society.

IEEE Women in Electron Devices Committee ( WiEDS ) Committee Member.

Education & Experience

Michelly de Souza received the Electrical Engineering degree from Centro Universitario FEI in 2002. She received the M.Sc. and Ph. D. degrees in 2005 and 2008, respectively, in Electrical Engineering (Microelectronics) from Politechnical School of University of São Paulo, Brazil. From September 2007 to February 2008 she was with Laboratoire de Microélectronique from Université Catholique de Louvain (UCLouvain), Belgium, working in the fabrication and electrical characterization of Silicon-On-Insulator (SOI) transistors.From 2008 to 2013 she was with FEI, where she worked as a post-doctoral researcher. Since 2013 she joined FEI faculty staff, where she is now Full Professor at Electrical Engineering Department.

Dr. Michelly de Souza is Senior Member of the IEEE and Brazilian Microelectronics Society. She is also Researcher Associated to the National Council for Scientific Development (CNPq), Brazil. She is author or co-author of more than 150 technical papers in peer-reviewed journals and conferences.

Her current interests are the electrical characterization and simulation of advanced SOI CMOS devices; low-power applications and temperature influence on the of operation of SOI devices.

Scientific Research Activities

Research Projects

(work on and/or manage)2020 - 2023 - Evaluation of Advanced Semiconductor Devices as a Function of the Temperature aiming at IoT Applications.

Coordinator: Michelly de Souza

Sponsored by: CNPq - Conselho Nacional de Desenvolvimento Científico e Tecnológico

2017 - 2022 - Use of SOI Devices for Low Power Applications

Coordinator: Michelly de Souza

Sponsored by: CNPq - Conselho Nacional de Desenvolvimento Científico e Tecnológico

2020 - 2022 - Atomistic Simulation of the Electrical Properties of MOS Transistor Nanowires

Coordinator: Marcelo Antonio Pavanello

Sponsored by: FAPESP - Fundação de Amparo à Pesquisa do Estado de São Paulo

2020 - 2024 - Training Doctors in Electrical Engineering in Health and Energy Areas

Coordinator: Marcelo Antonio Pavanello

Sponsored by: CNPq - Conselho Nacional de Desenvolvimento Científico e Tecnológico

Research Lines

Electrical Characterization and Numerical Simulation of Semiconductor Devices

Semiconductor Devices for Low-Power Low Voltage Applications

Nanometric Multiple-Gate SOI Transistores

Temperature Effect on Semiconductor Devices

Research Team

Publications

List with all my publications can be found at

Journal Papers

1.BERGAMASCHI, F. E. ; RIBEIRO, T. A. ; PAZ, B. C. ; SOUZA, Michelly de ; BARRAUD, S. ; CASSE, M. ; VINET, M. ; FAYNOT, O. ; PAVANELLO, Marcelo A. . Experimental Demonstration of Ω-Gate SOI Nanowire MOS Transistors? Mobility Variation Induced by Substrate Bias. IEEE TRANSACTIONS ON ELECTRON DEVICES, v. 69, p. 4022-4028, 2022. http://dx.doi.org/10.1109/TED.2022.3177393

2. PAVANELLO, Marcelo A. ; SOUZA, Michelly de . Performance of SOI Ω-Gate Nanowires from Cryogenic to High Temperatures. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 17, p. 1-8, 2022. http://dx.doi.org/10.29292/jics.v17i2.621

3. TREVISOLI, R D ; PAVANELLO, Marcelo A. ; DORIA, Rodrigo Trevisoli ; CAPOVILLA, Carlos E. ; BARRAUD, SYLVAIN ; DE SOUZA, MICHELLY . Variability Modeling in Triple-Gate Junctionless Nanowire Transistors. IEEE Transactions on Electron Devices, v. 69, p. 4730-4736, 2022. http://dx.doi.org/10.1109/ted.2022.3180303

4. DE SOUZA, MICHELLY; Doria, Rodrigo Trevisoli ; TREVISOLI, RENAN ; BARRAUD, SYLVAIN ; ANTONIO PAVANELLO, MARCELO . On the Application of Junctionless Nanowire Transistors in Basic Analog Building Blocks. IEEE Transactions on Nanotechnology, v. 20, p. 234-242, 2021. http://dx.doi.org/10.1109/TNANO.2021.3058885

5. SILVA, L. M. B. ; PAZ, Bruna Cardoso ; DE SOUZA, MICHELLY . Analysis of Mobility in Graded-Channel SOI Transistors aiming at Circuit Simulation. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 15, p. 1-5, 2020. https://doi.org/10.29292/jics.v15i2.188

6. RODRIGUES, Edson J. ; DE SOUZA, MICHELLY . Temperature, Silicon Thickness and Intrinsic Length Influence on the Operation of Lateral SOI PIN Photodiodes. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 15, p. 1-5, 2020. https://doi.org/10.29292/jics.v15i2.158

7. RODRIGUES DA SILVA, PAULO ; de Souza, Michelly . Analysis of Current Mirrors with Asymmetric Self-Cascode Association of SOI MOSFETs through SPICE Simulations. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 15, p. 1-5, 2020. https://doi.org/10.29292/jics.v15i2.159

8. MARTINS D'OLIVEIRA, LI'GIA ; KILCHYTSKA, Valeriya ; FLANDRE, Denis ; de Souza, Michelly . Self-Cascode Current-Voltage Curve-Construction Algorithm from Single MOSFET Measurements for Analog Figures-of-Merit Extraction. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 14, p. 1-6, 2019. https://doi.org/10.29292/jics.v14i1.69

9. TREVISOLI, Renan D. ; DORIA, RODRIGO T. ; SOUZA, Michelly de ; BARRAUD, SYLVAIN ; PAVANELLO, Marcelo A. . Junctionless Nanowire Transistors Parameters Extraction Based on Drain Current Measurements. SOLID-STATE ELECTRONICS, v. 158, p. 37-45, 2019. http://dx.doi.org/10.1016/j.sse.2019.05.004

10. Pavanello, Marcelo Antonio ; TREVISOLI, RENAN ; Doria, Rodrigo Trevisoli ; de Souza, Michelly . Static and dynamic compact analytical model for junctionless nanowire transistors. JOURNAL OF PHYSICS-CONDENSED MATTER, v. 30, p. 334002, 2018. http://dx.doi.org/10.1088/1361-648x/aad34f

11. Doria, Rodrigo Trevisoli ; TREVISOLI, RENAN ; de Souza, Michelly ; Pavanello, Marcelo Antonio . Physical Insights on the Dynamic Response of SOI n- and p-Type Junc-tionless Nanowire Transistors. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 13, p. 1-7, 2018. http://dx.doi.org/10.29292/jics.v13i1.17

12. ASSALTI, Rafael ; FLANDRE, Denis ; de Souza, Michelly . Influence of Geometrical Parameters on the DC Analog Behavior of the Asymmetric Self-Cascode FD SOI nMOSFETs. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 13, p. 1-7, 2018. http://dx.doi.org/10.29292/jics.v13i2.15

13. ALVES, C. R. ; FLANDRE, Denis ; DE SOUZA, MICHELLY . Analysis of Mismatching on the Analog Characteristics of GC SOI MOSFETs. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 13, p. 1-8, 2018. http://dx.doi.org/10.29292/jics.v13i3.16

14. TREVISOLI, RENAN ; Doria, Rodrigo Trevisoli ; SOUZA, Michelly de ; BARRAUD, SYLVAIN ; VINET, MAUD ; CASSE, MIKAEL ; REIMBOLD, GILLES ; FAYNOT, OLIVIER ; GHIBAUDO, GERARD ; PAVANELLO, Marcelo A. . A New Method for Series Resistance Extraction of Nanometer MOSFETs. IEEE TRANSACTIONS ON ELECTRON DEVICES, v. 64, p. 2797-2803, 2017. http://dx.doi.org/10.1109/TED.2017.2704928

15. DORIA, Rodrigo Trevisoli ; TREVISOLI, Renan D. ; SOUZA, Michelly de ; VINET, MAUD ; BARRAUD, SYLVAIN ; PAVANELLO, Marcelo A. . Analysis of the substrate bias effect on the interface trapped charges in junctionless nanowire transistors through low-frequency noise characterization. MICROELECTRONIC ENGINEERING, v. 178, p. 17-20, 2017. http://dx.doi.org/10.1016/j.mee.2017.04.014

16. DORIA, R.T. ; FLANDRE, D. ; TREVISOLI, R D ; SOUZA, Michelly de ; PAVANELLO, Marcelo A. . Effect of the Back Bias on the Analog Performance of Standard FD and UTBB Transistors-Based Self-Cascode Structures. Semiconductor Science and Technology, v. 32, p. 1-10, 2017. http://dx.doi.org/10.1088/1361-6641/aa7659

17. ASSALTI, R. ; DORIA, RODRIGO T. ; FLANDRE, Denis ; SOUZA, Michelly de . Origin of the Low-Frequency Noise in the Asymmetric Self-Cascode Structure Composed by Fully Depleted SOI nMOSFETs. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 12, p. 62-70, 2017. http://dx.doi.org/10.29292/jics.v12i2.452

18. TREVISOLI, Renan D. ; DORIA, RODRIGO T. ; SOUZA, Michelly de ; BARRAUD, S. ; VINET, M. ; PAVANELLO, MARCELO A. . Analytical Model for the Dynamic Behaviour of Triple-Gate Junctionless Nanowire Transistors. IEEE Transactions on Electron Devices, v. 63, p. 856-863, 2016. http://dx.doi.org/10.1109/TED.2015.2507571

19. ASSALTI, R. ; D'OLIVEIRA, L. M. ; PAVANELLO, Marcelo A. ; FLANDRE, Denis ; SOUZA, Michelly de . Experimental and simulation analysis of electrical characteristics of common-source current mirrors implemented with asymmetric self-cascode silicon-on-insulator n-channel metal-oxide-semiconductor field-effect transistors. IET Circuits, Devices & Systems (Print), v. 1, p. 1, 2016. http://dx.doi.org/10.1049/iet-cds.2015.0159

20. SOUZA, Michelly de; FLANDRE, Denis ; Doria, Rodrigo Trevisoli ; TREVISOLI, RENAN ; PAVANELLO, Marcelo A. . On the improvement of DC analog characteristics of FD SOI transistors by using asymmetric self-cascode configuration. Solid-State Electronics, v. 117, p. 152-160, 2016. http://dx.doi.org/10.1016/j.sse.2015.11.018

21. TREVISOLI, RENAN ; DE SOUZA, MICHELLY ; Doria, Rodrigo Trevisoli ; KILCHTYSKA, VALERIYA ; FLANDRE, Denis ; Pavanello, Marcelo Antonio . Junctionless nanowire transistors operation at temperatures down to 4.2 K. Semiconductor Science and Technology (Print), v. 31, p. 114001, 2016. http://dx.doi.org/10.1088/0268-1242/31/11/114001

22. PAVANELLO, Marcelo A. ; SOUZA, Michelly de ; RIBEIRO, Thales Augusto ; MARTINO, João Antonio ; FLANDRE, D. . Improved operation of graded-channel SOI nMOSFETs down to liquid helium temperature. Semiconductor Science and Technology (Print), v. 31, p. 114005, 2016. http://dx.doi.org/10.1088/0268-1242/31/11/114005

23. TREVISOLI, RENAN ; Doria, Rodrigo Trevisoli ; DE SOUZA, MICHELLY ; Pavanello, Marcelo Antonio . Extraction of the interface trap density energetic distribution in SOI Junctionless Nanowire Transistors. Microelectronic Engineering, v. 147, p. 23-26, 2015. http://dx.doi.org/10.1016/j.mee.2015.04.040

24. CERDEIRA, Antonio ; AVILA, F. ; IÑIGUEZ, Benjamín ; DE SOUZA, MICHELLY ; PAVANELLO, Marcelo Antonio ; ESTRADA, Magali . Compact core model for Symmetric Double-Gate Junctionless Transistors. Solid-State Electronics, v. 94, p. 91-97, 2014. http://dx.doi.org/10.1016/j.sse.2014.02.011

25. TREVISOLI, Renan Doria ; DORIA, Rodrigo Trevisoli ; DE SOUZA, MICHELLY ; PAVANELLO, Marcelo Antonio . Substrate Bias Influence on the Operation of Junctionless Nanowire Transistors. IEEE Transactions on Electron Devices, v. 61, p. 1575-1582, 2014. http://dx.doi.org/10.1109/TED.2014.2309334

26. DORIA, Rodrigo Trevisoli ; TREVISOLI, Renan D. ; SOUZA, Michelly de ; PAVANELLO, Marcelo Antonio . Low-frequency noise and effective trap density of short channel p- and n-types junctionless nanowire transistors. Solid-State Electronics, v. 96, p. 22-26, 2014. http://dx.doi.org/10.1016/j.sse.2014.04.019

27. DORIA, Rodrigo Trevisoli ; TREVISOLI, Renan Doria ; SOUZA, Michelly de ; CUETO, Magali Estrada ; CERDEIRA, Antonio ; PAVANELLO, Marcelo A. . The Roles of the Gate Bias, Doping Concentration, Temperature and Geometry on the Harmonic Distortion of Junctionless Nanowire Transistors Operating in the Linear Regime. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 9, p. 110-117, 2014. http://dx.doi.org/10.29292/jics.v9i2.396

28. SOUZA, Michelly de; TREVISOLI, Renan D. ; DORIA, Rodrigo Trevisoli ; PAVANELLO, Marcelo Antonio . A physically-based threshold voltage definition, extraction and analytical model for junctionless nanowire transistors. Solid-State Electronics, v. 90, p. 12-17, 2013. http://dx.doi.org/10.1016/j.sse.2013.02.059

29. SOUZA, Michelly de; PAZ, Bruna Cardoso ; FLANDRE, Denis ; PAVANELLO, Marcelo Antonio . Asymmetric channel doping profile and temperature reduction influence on the performance of current mirrors implemented with FD SOI nMOSFETs. Microelectronics and Reliability, p. 848-855, 2013. http://dx.doi.org/10.1016/j.microrel.2013.03.005

30. CERDEIRA, A. ; ESTRADA, M. ; INIGUEZ, B. ; TREVISOLI, R.D. ; DORIA, R.T. ; DE SOUZA, M. ; PAVANELLO, M.A. . Charge-based continuous model for long-channel Symmetric Double-Gate Junctionless Transistors. Solid-State Electronics, v. 85, p. 59-63, 2013. http://dx.doi.org/10.1016/j.sse.2013.03.008

31. DORIA, Rodrigo Trevisoli ; TREVISOLI, Renan Doria ; DE SOUZA, MICHELLY ; PAVANELLO, Marcelo Antonio . Trap density characterization through low-frequency noise in junctionless transistors. Microelectronic Engineering, v. 109, p. 79-82, 2013. http://dx.doi.org/10.1016/j.mee.2013.03.090

32. ORTIZ-CONDE, Adelmo ; GARCIA-SANCHEZ, Francisco ; BARRIOS, Alberto Terán ; MUCI, Juan ; DE SOUZA, MICHELLY ; PAVANELLO, Marcelo Antonio . Approximate analytical expression for the terminal voltage in multi-exponential diode models. Solid-State Electronics, v. 89, p. 7-11, 2013. http://dx.doi.org/10.1016/j.sse.2013.06.010

33. TREVISOLI, Renan D. ; DORIA, Rodrigo Trevisoli ; DE SOUZA, MICHELLY ; PAVANELLO, Marcelo Antonio . Drain Current and Short Channel Effects Modeling in Junctionless Nanowire Transistors. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 8, p. 116-124, 2013. http://dx.doi.org/10.29292/jics.v8i2.382

34. TREVISOLI, Renan D. ; DORIA, Rodrigo Trevisoli ; DE SOUZA, MICHELLY ; PAVANELLO, Marcelo Antonio . Analysis of the leakage current in junctionless nanowire transistors. Applied Physics Letters, v. 103, p. 202103, 2013. http://dx.doi.org/10.1063/1.4829465

35. PAVANELLO, Marcelo Antonio ; SOUZA, Michelly de ; Martino, Joao Antonio ; SIMOEN, Eddy ; CLAEYS, Cor . Analysis of temperature variation influence on the analog performance of 45° rotated triple-gate nMuGFETs. Solid-State Electronics, v. 70, p. 39-43, 2012. http://dx.doi.org/10.1016/j.sse.2011.11.014

36. TREVISOLI, Renan D. ; DORIA, Rodrigo Trevisoli ; SOUZA, Michelly de ; DAS, Samaresh ; FERAIN, I. ; PAVANELLO, Marcelo Antonio . The Zero Temperature Coefficient in Junctionless Nanowire Transistors. Applied Physics Letters, v. 101, p. 062101, 2012. http://dx.doi.org/10.1063/1.4744965

37. LUGO-MUÑOZ, Denise ; MUCI, Juan ; ORTIZ-CONDE, Adelmo ; GARCIA-SANCHEZ, Francisco ; SOUZA, Michelly de ; FLANDRE, Denis ; PAVANELLO, Marcelo Antonio . Modeling of Thin-Film Lateral SOI PIN Diodes with an Alternative Multi-Branch Explicit Current Model. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 7, p. 92-99, 2012. http://dx.doi.org/10.29292/jics.v7i2.360

38. DORIA, Rodrigo Trevisoli ; TREVISOLI, Renan D. ; SOUZA, Michelly de ; PAVANELLO, Marcelo Antonio . Impact of the Series Resistance in the I-V Characteristics of Junctionless Nanowire Transistors and its dependence on the Temperature. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 7, p. 121-129, 2012. http://dx.doi.org/10.29292/jics.v7i2.364

39. TREVISOLI, Renan D. ; DORIA, Rodrigo Trevisoli ; SOUZA, Michelly de ; DAS, Samaresh ; FERAIN, I. ; PAVANELLO, Marcelo Antonio. Surface Potential-Based Drain Current Analytical Model for Triple-Gate Junctionless Nanowire Transistors. IEEE Transactions on Electron Devices, v. 50, p. 3510-3518, 2012. http://dx.doi.org/10.1109/TEd.2012.2219055

40. DORIA, Rodrigo Trevisoli ; PAVANELLO, Marcelo Antonio ; TREVISOLI, Renan D. ; SOUZA, Michelly de ; LEE, C.-W. ; FERAIN, I. ; DEHDASHTI-AKHAVAN, N. ; YAN, R. ; RAZAVI, P. ; YU, R. ; KRANTI, A. ; COLINGE, J.-P. . Junctionless Multiple Gate Transistors for Analog Applications. I.E.E.E. Transactions on Electron Devices, v. 58, p. 2511-2519, 2011. http://dx.doi.org/10.1109/TED.2011.2157826

41. LUGO-MUÑOZ, Denise ; MUCI, Juan ; ORTIZ-CONDE, Adelmo ; GARCÏA-SÁNCHEZ, Francisco J. ; SOUZA, Michelly de ; PAVANELLO, Marcelo Antonio . An explicit multi-exponential model for semiconductor junctions with series and shunt resistances. Microelectronics and Reliability, v. 51, p. 2044-2048, 2011. http://dx.doi.org/10.1016/j.microrel.2011.06.030

42. SOUZA, Michelly de; BULTEEL, Olivier ; FLANDRE, Denis ; PAVANELLO, Marcelo Antonio . Temperature and Silicon Film Thickness Influence on the Operation of Lateral SOI PIN Photodiodes for Detection of Short Wavelengths. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 6, p. 107-113, 2011. http://dx.doi.org/10.29292/jics.v6i2.346

43. DORIA, Rodrigo Trevisoli ; PAVANELLO, Marcelo Antonio ; TREVISOLI, Renan D. ; SOUZA, Michelly de ; LEE, C.-W. ; FERAIN, I. ; DEHDASHTI-AKHAVAN, N. ; YAN, R. ; RAZAVI, P. ; YU, R. ; KRANTI, A. ; COLINGE, J.-P. . Analog Operation Temperature Dependence of nMOS Junctionless Transistors Focusing on Harmonic Distortion. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 6, p. 114-121, 2011. http://dx.doi.org/10.29292/jics.v6i2.347

44. SOUZA, Michelly de; PAVANELLO, Marcelo Antonio ; TREVISOLI, Renan D. ; DORIA, Rodrigo Trevisoli ; COLINGE, J.-P. . Cryogenic Operation of Junctionless Nanowire Transistor. IEEE Electron Device Letters (Print), v. 32, p. 1322-1324, 2011. http://dx.doi.org/10.1109/LED.2011.2161748

45. TREVISOLI, Renan Doria ; DORIA, Rodrigo Trevisoli ; SOUZA, Michelly de ; PAVANELLO, Marcelo Antonio . Threshold voltage in junctionless nanowire transistors. Semiconductor Science and Technology (Print), v. 26, p. 105009, 2011. http://dx.doi.org/10.1088/0268-1242/26/10/105009

46. SOUZA, Michelly de; RUE, Bertrand ; FLANDRE, Denis ; PAVANELLO, Marcelo Antonio . Thin-Film Lateral SOI PIN Diodes for Thermal Sensing Reaching the Cryogenic Regime. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 5, p. 160-167, 2010. http://dx.doi.org/10.1016/j.mee.2007.04.116

47. SOUZA, Michelly de; FLANDRE, Denis ; PAVANELLO, Marcelo Antonio . Analysis of source-follower buffers implemented with graded-channel SOI nMOSFETs operating at cryogenic temperatures. Cryogenics (Guildford), v. 49, p. 599-604, 2009. http://dx.doi.org/10.1016/j.cryogenics.2008.12.010

48. SOUZA, Michelly de; FLANDRE, Denis ; PAVANELLO, Marcelo Antonio . Advantages of graded-channel SOI nMOSFETs for application as source-follower analog buffer. Solid-State Electronics, v. 52, p. 1933-1938, 2008. http://dx.doi.org/10.1016/j.sse.2008.06.047

49. SOUZA, Michelly de; FLANDRE, Denis ; PAVANELLO, Marcelo Antonio . Study of Matching Properties of Graded-Channel SOI MOSFETs. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 3, p. 69-75, 2008. http://dx.doi.org/10.29292/jics.v3i2.284

50. SOUZA, Michelly de; PAVANELLO, Marcelo Antonio ; MARTINO, João Antonio ; SIMOEN, Eddy ; CLAEYS, Cor . Low temperature influence on the uniaxially strained FD SOI nMOSFETs behavior. Microelectronic Engineering, v. 84, p. 2121-2124, 2007. http://dx.doi.org/10.1016/j.mee.2007.04.116

51. SOUZA, Michelly de; PAVANELLO, Marcelo Antonio . Charge-Based Continuous Equations for the Transconductance and Output Conductance of Graded-Channel SOI MOSFETs. JICS. JOURNAL OF INTEGRATED CIRCUITS AND SYSTEMS (ED. PORTUGUÊS), v. 2, p. 104-110, 2007. https://doi.org/10.29292/jics.v2i2.274

52. SOUZA, Michelly de; PAVANELLO, Marcelo Antonio ; IÑIGUEZ, Benjamín ; FLANDRE, Denis . A Charge-Based Continuous Model for Submicron Graded-Channel nMOSFET for Analog Circuit Simulation. Solid-State Electronics, Oxford, v. 49, n.10, p. 1683-1692, 2005. http://dx.doi.org/10.1016/j.sse.2005.08.00

Infrastructure

LNCI - Laboratory of Nanoelectronics and Integrated Circuits

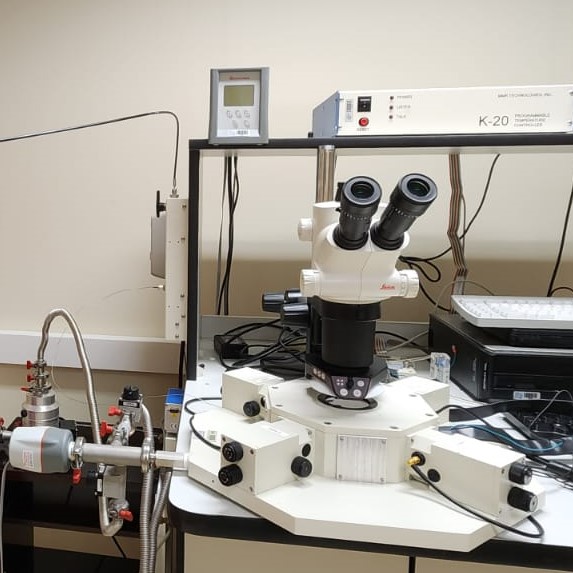

MMR Low Temperature MicroProbe System

The Joule-Thomson temperature stage inside the vaccum chamber provides both a cryogenic cooling and heating system to enable automated and high precision control of the temperature of the sample stage over a wide range of temperatures. K20 Temperature Controller provides accurate temperature measurement, precise and very stable temperature control, and easy-to-use data acquisition functions over the temperature range from 80K to 730K.

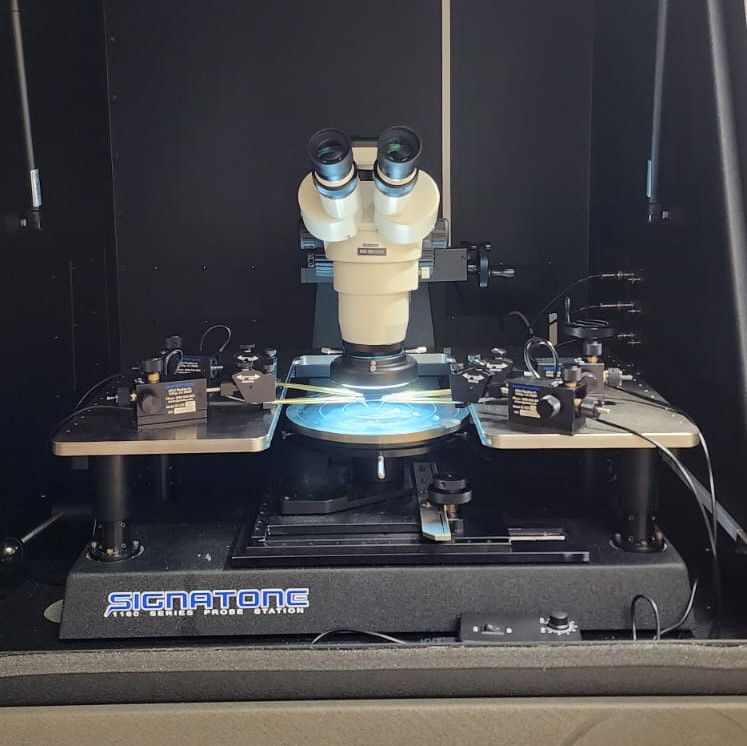

Signatone Manual Probe Station

Multi-purpose Manual Probe Station Model S-1160B-8N suitable for low-frequency measurements at room temperature.

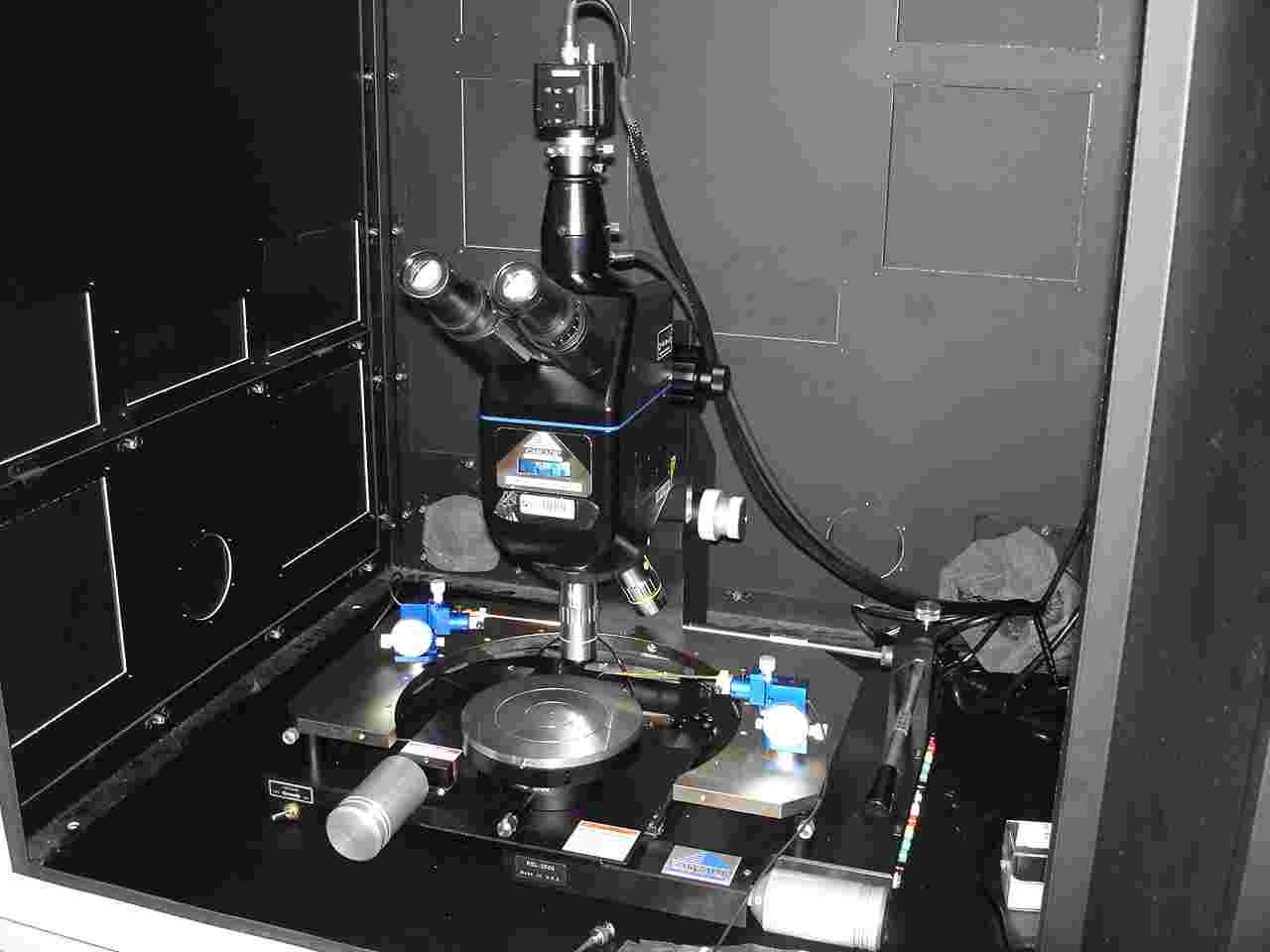

Cascade Manual Probe Station

Cascade Microtech Manual Probe Station Model REL 3600 suitable for low-frequency measurements at room temperature.

Keysight B1500A Semiconductor Parameter Analyzer

The Keysight B1500A semiconductor parameter analyzer is an all-in-one device characterization analyzer supporting IV, CV, pulse/dynamic IV.

Keithley 4200 Semiconductor Characterization System

Advanced measurement hardware for DC I-V, C-V, and pulsed I-V measurement types.

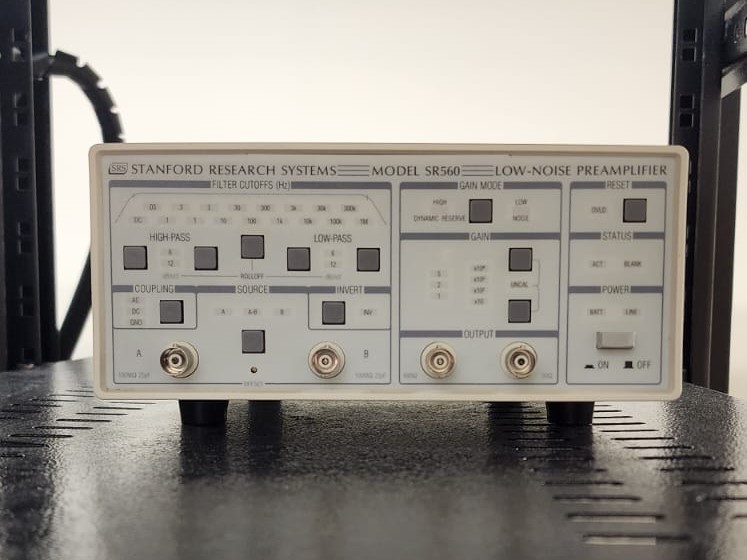

Low-Noise Amplifier

The SR560 architecture is diagrammed above. The instrument provides DCcoupled low-noise amplification of singleended and true differential input signals at gains of 1 to 50,000.

Laboratory of Simulation

The Laboratory of Simulation contains three workstations with the following tools:

Numerical Semiconductor Devices Simulators:

Semiconductor Process Technologies Simulators:

Teaching Activities

Undergraduate Courses

Electronics

Design of Integrated Circuits

Undergraduate Courses

Electrical Characterization of MOS Devices

Semiconductor Devices in SOI Technology

Simulation of Process and Electronic Devices

Contact

If you want to know more about my research and/or teaching activities, please send me a message.

e-mail: michelly@fei.edu.br

São Bernardo do Campo, SP, Brazil

CEP 09850-901